Section 8 - solutions

Section 8 - solutions.

Section 8 - solutions

E N D

Presentation Transcript

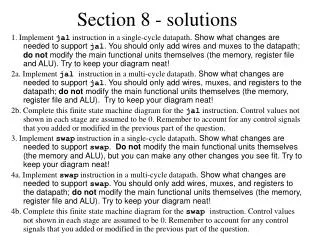

Section 8 - solutions 1. Implement jal instruction in a single-cycle datapath. Show what changes are needed to support jal. Youshould only add wires and muxes to the datapath; do not modify the main functional units themselves (thememory, register file and ALU). Try to keep your diagram neat! 2a. Implement jal instruction in a multi-cycle datapath. Show what changes are needed to support jal. Youshould only add wires, muxes, and registers to the datapath; do not modify the main functional units themselves (thememory, register file and ALU). Try to keep your diagram neat! 2b. Complete this finite state machine diagram for the jalinstruction. Control values not shown in each stage are assumed to be 0. Remember to account for any control signals that you added or modified in the previous part of the question. 3. Implement swap instruction in a single-cycle datapath. Show what changes are needed to support swap. Do not modify the main functional units themselves (thememory and ALU), but you can make any other changes you see fit. Try to keep your diagram neat! 4a. Implement swap instruction in a multi-cycle datapath. Show what changes are needed to support swap. Youshould only add wires, muxes, and registers to the datapath; do not modify the main functional units themselves (thememory, register file and ALU). Try to keep your diagram neat! 4b. Complete this finite state machine diagram for the swap instruction. Control values not shown in each stage are assumed to be 0. Remember to account for any control signals that you added or modified in the previous part of the question.

Notes about solutions Modifications to datapaths are done in colors. View them online if the handout is not clear. Sorry, we can’t make 100 colored handouts. Always read the question to determine what changes are allowed (note that problems 1 and 3 have different descriptions). It is OK to make any legal changes to datapaths, unless they are explicitly forbidden. For multi-cycle, correct FSM definition is important, because it enforces the order of operations. For single-cycle, everything happens simultaneously. For multi-cycle, it often helps to introduce additional registers to keep data temporarily for a cycle (see problem 4a). This doesn’t make sense for single-cycle. When adding new muxes, make the original input correspond to control signal ‘0’ (e.g. WrData1 in problem 3). Otherwise, all previously defined instructions could stop working. Adding new values to existing muxes may change the size of control signal of the mux (e.g. MemToReg in problem 4a). This sometimes requires making changes to the FSM definitions of existing instructions. It is often possible to perform multiple operations in a single cycle of the multi-cycle datapath. Minimizing the number of cycles is always a good approach, but it is usually not critical. Some operations just need to be done in sequence. First 2 cycles of the multi-cyle FSM are always the same. All instructions look the same until they are decoded.

Shift left 2 PC ALU Out IorD IRWrite RegWrite [31-26] [25-21] [20-16] [15-11] [15-0] Read register 1 Read data 1 ALU Read register 2 Zero Address Read data 2 Instruction register Result 0 M u x 1 2 0 M u x 1 0 M u x 1 2 0 M u x 1 0 M u x 1 2 Write register Memory ALUOp Memory data register A Write data Registers Write data Mem Data B bundle Sign extend 2a. jal – multi-cycle datapath PCWrite Upper 4 bits of PC ALUSrcA Lower 26 bits of instruction 00 RegDst MemRead 0 1 2 3 4 PCSource MemWrite 31 ALUSrcB MemToReg

2b. jal – modifications to control PCSource = 1 PCWrite = Zero

3. swap - single-cycle datapath 0 M u x 1 Add PC 4 Add Shift left 2 PCSrc RegWrite MemToReg MemWrite Read address Instruction [31-0] I [25 - 21] Read register 1 Read data 1 ALU Read address Read data 1 M u x 0 I [20 - 16] Zero Read register 2 Instruction memory Read data 2 0 M u x 1 Result Write address 0 M u x 1 Write Register 1 Data memory Write data Registers I [15 - 11] ALUOp Write Data 1 Write Register 2 Write Data 2 MemRead ALUSrc RegDst I [15 - 0] 1 M u x 0 Sign extend WrData1

4a. swap – multi-cycle datapath PCSource Shift left 2 ALUSrcA PC ALU Out IorD RegDst IRWrite RegWrite [31-26] [25-21] [20-16] [15-11] [15-0] Read register 1 Read data 1 ALU Read register 2 Zero Address Read data 2 Instruction register Result 0 M u x 1 0 M u x 1 2 3 0 M u x 1 0 M u x 1 0 M u x 1 Write register Memory ALUOp Memory data register A Write data Registers Write data Mem Data B Sign extend PCWrite MemRead 0 1 2 3 4 MemWrite ALUSrcB MemToReg Temp

4b. swap - modifications to control IorD = 0 MemRead = 1 IRWrite = 1 ALUSrcA = 0 ALUSrcB = 01 ALUOp = 010 PCSource = 0 PCWrite = 1 ALUSrcA = 1 ALUSrcB = 00 ALUOp = 110 PCSource = 1 PCWrite = Zero ALUSrcA = 0 ALUSrcB = 11 ALUOp = 010 RegDst = 1 MemToReg = 00 RegWrite = 1 ALUSrcA = 1 ALUSrcB = 00 ALUOp = func ALUSrcA = 1 ALUSrcB = 10 ALUOp = 010 IorD = 1 MemWrite = 1 RegDst = 0 MemToReg = 01 RegWrite = 1 RegDst = 0 RegWrite MemToReg = 11 RegDst = 1 RegWrite MemToReg = 10 Op = SWAP IorD = 1 MemRead = 1 Branch completion Op = BEQ R-type execution R-type writeback Instruction fetch and PC increment Register fetch and branch computation Op = R-type Memory write Effective address computation Op = SW Op = LW/SW Memory read lw register write Op = LW