General Description Silicon Detectors Electronics Electrical Tests Module Assembly

The Construction Status of the ATLAS Silicon Microstrip Tracker D. Ferr è re on behalf of the SCT collaboration DPNC, University of Geneva. General Description Silicon Detectors Electronics Electrical Tests Module Assembly Summary & Status. Atlas at LHC.

General Description Silicon Detectors Electronics Electrical Tests Module Assembly

E N D

Presentation Transcript

The Construction Status of the ATLAS Silicon Microstrip TrackerD. Ferrère on behalf of the SCT collaborationDPNC, University of Geneva • General Description • Silicon Detectors • Electronics • Electrical Tests • Module Assembly • Summary & Status Didier Ferrère, Geneva University Como, October 2001

Atlas at LHC LHC will provide protons and ions collisions Atlas A designed luminosity of 1034 cm-2s-1 p-p collision with 14 TeV in the center of mass Didier Ferrère, Geneva University Como, October 2001

The Atlas Detector Didier Ferrère, Geneva University Como, October 2001

Physics Motivations • Requires a good tracking performance: • Secondary vertices • Impact parameters resolution • Track isolation • Measurement of high momentum particles • Higgs in SM and in MSSM • Supersymmetric Particles • B physics (CP violation, ...) • Exotic physics Simulated Event in the Inner Detector Didier Ferrère, Geneva University Como, October 2001

SCT Environment • 23 overlapping interactions every bunch crossing (at the full Luminosity) • A bunch-bunch crossing every 25ns (40MHz) • Maximum equivalent 1 MeV neutron fluence after 10 years is ~ 2.1014 n/cm2 • Operating temperature on silicon detectors is -7oC to contain the reverse annealing and the leakage current • Maintenance will likely require yearly warm-up of 2 days at 20oC and 2 weeks at 17oC • Material < 0.4 X0 at the outer SCT envelope • Operation in a 2 Tesla solenoid field Didier Ferrère, Geneva University Como, October 2001

SCT in the Inner Detector • SCT: • 4 Barrels + 2x9 wheels • 4 different module types in the wheels • h < 2.5 Didier Ferrère, Geneva University Como, October 2001

The SCT Semiconductor Tracker Barrel diameters: B3: 568 mm B4: 710 mm B5: 854 mm B6: 996 mm 4088 Modules ~ 61 m2 of silicon 15,392 silicon wafers ~ 6.3 million of readout channels 5.6 m 1.04 m 1.53 m 9 wheels 4 barrels 9 wheels Didier Ferrère, Geneva University Como, October 2001

The SCT module types 2112 Barrel modules 936 Outer Forward Modules 640 Middle Forward Modules (incl. 80 Short Middle) 400 Inner Forward Modules Barrel Didier Ferrère, Geneva University Como, October 2001

Module Pictures • A Barrel Module • 2 daisy chained detectors / side • The Kapton hybrid is bridged • over the detectors • The cooling pipe is on the connector • side • An Outer Forward Module • 2 daisy chained detectors / side • The Kapton hybrid is at the far end • The cooling area is common with • the mounting blocks Didier Ferrère, Geneva University Como, October 2001

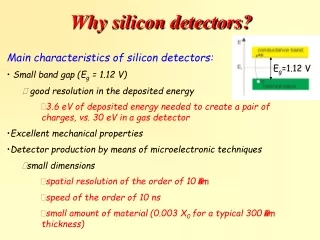

1 Barrel detector type 5 Forward detector types: W12: Inner Module W21 & W22: Middle Module W31 & W32: Outer Module Silicon Detector Pictures Single sided p-in-n detectors 768 strips Size ~ 6x6 cm2 285 mm thick • Barrel Pitch : 80 mm • Forward Pitch: • W31 and W32: 161.5 mrad • W12, W21 & W22: 207 mrad Scratch pads for identification – Corresponds to DB serial number Didier Ferrère, Geneva University Como, October 2001

Silicon Detector Status The detectors passed the Production Readiness Review in August 2000. The production delivery started this year. The detector purchases is distributed as followed: * On going qualification Delivery status of Hamamatsu detectors in Geneva University Didier Ferrère, Geneva University Como, October 2001

Silicon Detector – Some Specifications • Total leakage currentat 20 oC: <6 mA@150V and <20 mA@350V • Leakage current stability: to increase by not more than 2 mA @150V in dry air over 24 hours • Depletion Voltage< 150V • R bias= 1.25 +/- 0.75 MW (Poly-silicon or implanted technology) • C coupling>= 20 pF/cm @ 1kHz • C interstrip< 1.1pF/cm @ 100kHz @ 150V bias • R interstrip>2x R bias at operating voltage • Strip metal resistance<15 W/cm • Strip quality: a mean of >99% good readout strips per delivery batch. Not less that 98% /detector Pre-Irradiation Post-Irradiation • Total leakage current <250 mA up to 450V @ -18 oC • Leakage Current stability:to vary by no more than 3% in 24 hours at 350V at -10 oC • Strip defects: Number of strip defects (dielectric & metal) within pre-irradiation acceptance level • Charge collection: Maximum operating voltage for >90% of maximum achievable charge : 350V Didier Ferrère, Geneva University Como, October 2001

Quality Control consists of systematic checks for Visual Inspection and IV scan & sub-sample tests (10% of the detectors): Depletion voltage, full strip test, metal strip resistance and Interstrip capacitance Silicon Detector Quality Control Up to now only few rejections has been made based on visual defects and extra currents. Example of W31 normalized current @ 20oC nA Didier Ferrère, Geneva University Como, October 2001

Silicon Detector Quality Control 0.082 % of detective strips out of 172 detectors The defective strips are identified by Hamamatsu and the QC at the Institutes. The full strip test allows to identify all possible defects like: Open, Short, bias resistor break, pin hole, oxide punch through, implant break. The detectors are slightly biased during the measurement and up to 100V DC is put on the strips. LCR meter allows to measure coupling capacitance and the relative bias resistor. 0.044 % of detective strips out of 170 detectors Hamamatsu series production delivered in Geneva Didier Ferrère, Geneva University Como, October 2001

Silicon Detector – Irradiation The detectors are irradiated using 24 GeV protons at CERN PS. All strips are grounded and the backplane is biased to 100V during the irradiation. Typical annealing is done at the minimum of the beneficial and reverse annealing. mA V Didier Ferrère, Geneva University Como, October 2001

Silicon Detector – Charge Collection after Irradiation Barrel The detectors were annealed 7 days at 25oC after an irradiation of 3x1014 p/cm2 The readout was made with SCT 128A chips (DMILL technology). A Ru106 source was used for the injected charge. The Signal to noise ratio is for a strip length of ~6 cm The measurement was taken at –18oC W31 D. Robinson 350V A S/N plateau around 17:1 is reached above 350V for all the Hamamatsu detectors W32 Similar results are obtained for the other detector purchases Didier Ferrère, Geneva University Como, October 2001

Binary ABCD chips are based on DMILL BiCMOS technology The Front End Electronics • Noise with detectors (12 cm strips): < 1500 e- • Efficiency: 99% • Occupancy due to Noise : 5x10-4 • Double pulse resolution: 50ns for 3.5fC following 3.5 fC signal • Shaping time ~ 20 ns • Pipeline Length: 3.2 ms (128 locations) • Functionality temperature range: -15 to 30oC • Power dissipation: < 3.8 mW/channel • Specified total radiation dose: 2x1014 n/cm2 • 10 Mrad Didier Ferrère, Geneva University Como, October 2001

ABCD 3T – Trimming function The Front End Electronics The readout chips passed the PRR in July 2001. Pre-series have started with 35 wafers already delivered. In November 200 wafers are expected. The measured yield on the pre-series is spread from 10 to 50 % and the expected yield in average is ~26%. ATMEL think they can improve it! • Yield consideration based on: • All analog and digital functionalities are OK (tested with threshold, bias and frequency scan) • No Icc or Idd problem • No bad channels The wafer screening for the Quality Control will be done at 3 places: CERN, RAL and SCIPP. Current testing time ~9 hours/wafer Will be decrease during prod by a factor 2 Didier Ferrère, Geneva University Como, October 2001

The Module Test Set-up The SCT DAQ (software and hardware) readout test set-up is the same in all the laboratories. • Tests on modules: • Measured gain curve (with internal calibration signal) • Hit occupancy versus comparator threshold without signal (“Noise Occupancy”) • Determination of ENC (from response curve and Noise Occupancy) • Pulse shape through variation of calibration pulse delay • Power consumption at different settings • Various digital function checks (pipeline & data transfer) Didier Ferrère, Geneva University Como, October 2001

Signal and ENC determination • “S-curves”: • Measure hit occupancy as a function of the threshold • Fit error function to occupancy “S-curve” • Determines mean signal & rms Didier Ferrère, Geneva University Como, October 2001

Module Performances • Pre-irradition • ENC noise: 1400-1500e- • NO @1fC: 1-2 x 10-5 • Post-irradition • ENC noise: 1900e- • NO @1fC: 2-3 x 10-4 * 5x10-4 * Acceptance criteria : 5x10-4 Didier Ferrère, Geneva University Como, October 2001

KEK Test Beam – Median Charge Preliminary results from N. Unno A small difference between barrel and end-cap modules is observed and could be due to: Larger effective pitch for the forward and less charge sharing. (V) Barrel and End-cap modules are functioning well and are very similar Didier Ferrère, Geneva University Como, October 2001

KEK Test Beam – Efficiency and Noise Occupancy Preliminary results from N. Unno Specs Didier Ferrère, Geneva University Como, October 2001

Test Beam Results – Spatial Resolution Spatial resolution in strip coodinate (+/- 20mrad stereo angle) 23mm compatible with digital resolution for 80mm pitch • Gives spatial resolution in X/Y • s(X) = 20mm • s(Y) = 750mm Didier Ferrère, Geneva University Como, October 2001

Multiple Modules in the System Test • Determine performance of individual modules • Measure noise and “inter-module” effects • Optimize grounding and shielding in realistic setup Didier Ferrère, Geneva University Como, October 2001

Noise Performance in the System Test Tests on multi-modules barrel setup Didier Ferrère, Geneva University Como, October 2001

Noise Comparison System Test versus Single Module Test ENC System TestENC Individual Module ENC Noise Occupancy Didier Ferrère, Geneva University Como, October 2001

Barrel alignment system Module Assembly Aligned forward detector pairs onto transfer plates Parallel module production will take place Barrel: KEK, RAL, LBL, Oslo – Starting at the end of this year Forward: Freiburg, Geneva, Melbourne, Nikhef, MPI, UK-North, Valencia Didier Ferrère, Geneva University Como, October 2001

Module Mechanical Tolerances SCT Philosophy: Build modules to a sufficiently high tolerance that alignment corrections “within the module” are not needed for track reconstruction Physics requirement:Alignment accuracy rms (in micron) Internal module build tolerances:Alignment tolerance (in micron) Didier Ferrère, Geneva University Como, October 2001

Engineering Barrel sector close-up view of brackets, pipes, modules… Forward disc sector Middle cooling circuits, cooling blocks and low mass tapes Barrel support structure is under construction Forward support structure is ready for FDR Didier Ferrère, Geneva University Como, October 2001

Summary and Status • Detectors • The series production started beginning of 2001 and is well on the way • ~ 36% of the detectors are delivered and the quality is very good • Chips • ABCD3T passed production readiness review and first lot of production wafers • are expected soon • Modules • Barrel modules passed FDR and will start production at the end of the year • Forward modules require 1 more round of hybrid production before going to FDR • Engineering, Off-detector Components, power distribution • A series of FDRs started in spring • First parts are/will be soon order for production Didier Ferrère, Geneva University Como, October 2001

Appendix - Typical Power Consumption Module current and power • ICC after irradiation due to the optimization of the FE setting: • before irr: Ipre = 220 mA and Ishap = 30 mA • after irr: Ipre = 150 mA and Ishap = 24 mA Didier Ferrère, Geneva University Como, October 2001

Appendix – Prototype Components of the Forward Modules Spine Kapton Hybrid Didier Ferrère, Geneva University Como, October 2001

Appendix – Optical Links Opto-packages on the dog-leg (Barrel) Forward Opto-plug-in: PIN receiver (Clock & Control BPM) & 2 VCSEL lasers for data links Didier Ferrère, Geneva University Como, October 2001

Appendix – Forward Electrical Performances From G.Moorhead Didier Ferrère, Geneva University Como, October 2001

Appendix – Forward Electrical Performances From G.Moorhead Didier Ferrère, Geneva University Como, October 2001

Appendix – Thermal Simulation • Requirement:Prevent Thermal Runaway • Facts of life: • Leakage current (4 detectors of the module) after 10 years in the LHC reaches ~2mA @ 500V @ -10 ° C (spec: <1. 0mA @450V @- 18 ° C) • Increased ASIC power estimates: now 6.8W per module • ASICs are close to detector and module designs are optimized to limit heat transfer to detectors. • Some thermal design features: • Baseboard or spine are made of TPG (Thermo Pyrolitic Graphite). Conductivity: 1700 W/ m/ K along length • Improved hybrid substrate (metallised CF or CC) reduces hybrid & ASIC temperatures, reducing convection (~ 0.5W with CF) • Evaporative C3F8 cooling - extensive system prototyping has been done. It looks promising using -20 ° C at the cooling block Didier Ferrère, Geneva University Como, October 2001

Appendix – Thermal Simulation Didier Ferrère, Geneva University Como, October 2001

Module Power Consumption After annealing (10 days continuous warm operation) @ 40MHz • observed on some modules increase of Idd current (up to x2 normal current) but still within specs for current and total module power (6.8W/module) • on effected module current comes from all chips uniformly • under investigation ... Didier Ferrère, Geneva University Como, October 2001