System Simulation

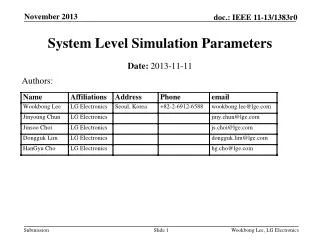

System Simulation. Objectives. After completing this module, you will be able to: Describe the functionality of SimGen Describe the integration of SimGen within XPS Describe the simulation process Describe what SmartModel™ Libraries are and how to use them. Outline. SimGen

System Simulation

E N D

Presentation Transcript

Objectives After completing this module, you will be able to: • Describe the functionality of SimGen • Describe the integration of SimGen within XPS • Describe the simulation process • Describe what SmartModel™ Libraries are and how to use them

Outline • SimGen • Simulation Procedure • SmartModel Libraries

SimGen • The Simulation Model Generation tool (SimGen) generates and configures various simulation models for the specified hardware • SimGen will generate simulation models by using a Microprocessor Hardware Specification (MHS) file • SimGen searches for input files in the following directories located in the project directory • <project_directory>/hdl/ • system_name.[vhd|v] • peripheral_wrapper.[vhd|v] • <project_directory>/implementation/ (if any of the peripherals are black-box) • peripheral_wrapper.ngc • system_name.ngc • system_name.ncd

project_directory simulation directory <Sim_model>* SimGen SimGen Generated Directories • SimGen produces • <peripheral_wrapper>.[vhd|v] *** • <system_name>.[vhd|v] • <system_name>.do • <system_name>_sim.bmm • <system_name>.sdf ** * <Sim_model> = behavioral/structural/timing ** <system_name>.sdf in timing simulation *** <peripheral_wrapper>.[vhd\v] in behavioral or structural simulation

executable.elf system.bmm system.[vhd|v] Data2MEM system_init.[vhd|v] Memory Initialization • To initialize memory in the simulation models created by SimGen, you need: • The compiled executable • executable.elf • The simulation hardware model generated by executing SimGen • system.vhd or system.v • The BMM file generated by PlatGen • <project_directory>/implementation directory

Memory Initialization • The system.bmm file is created by the PlatGen tool and carries block memory related information (see next slide) • Number of block memories • Address range for each set of block memory • Data indexing for each block memory in a set • The executable.elf file is generated by the compiler and carries data variables and code • The system.vhd file is generated by the SimGen tool and carries a hardware model of the system • The Data2MEM program uses the above mentioned files, extracts data code information, and generates a system_init.vhd file that contains block memory initialization content

Simulation Libraries: EDK • EDK library • Used for behavioral simulation • Contains all of the EDK IP components precompiled for ModelSim SE and PE • Not available for ModelSim XE • Only VHDL support • Must be compiled for the target simulator • Only the ModelSim simulator is supported • Compiling the EDK library by using COMPEDKLIB • compedklib [ -h ] [ -o output-dir-name ] [ -lp repository-dir-name ] [ -X compxlib-output-dir-name ] [ -E compedklib-output-dir-name ]

Simulation Libraries: XILINX • UNISIM library • Used for behavioral simulation and contains default unit delays • Includes all of the Xilinx Unified Library components that are inferred by most popular synthesis tools • SIMPRIM library • Used for structural and timing simulation • Includes all of the Xilinx Primitives Library components that are used by Xilinx implementation tools • XilinxCoreLib library • Contains pre-optimized modules to take advantage of architectural resources • Library models are used for behavioral simulation • May be used for your own defined IPs • Structural and timing simulation models generated by SimGen instantiate the SIMPRIM library components

Outline • SimGen • Simulation Procedure • SmartModel Libraries

1 Set up the Project Options Integration within XPS • Specify simulation parameters by usingOptions Project Options • HDL and Simulation tab • HDL • Simulator Compile Script • Simulation Libraries Path • EDK Library • XILINX Library • Simulation Models • Hierarchy and Flow tab • Submodule • ISE Flow • Projnav Directory

2 Generate the Simulation Model Integration within XPS • Generate the simulation models • Generation of simulation models:Tools Sim Model Generation • Generation of simulation models and simulation initialization:Tools Hardware Simulation (system model must be top-level)

4 3 Using Windows Explorer, double-click system.npl Copy the files to the ProjNav directory Export to ProjNav

5 Create/Add testbench file Use within the Project Navigator • VHDL • Using Project New Source VHDL Test Bench • Using Project Add Source, add the testbench to the project • Verilog • Using Project New Source Verilog Test Fixture • Using Project Add Source, add the testbench to the project

6 Copy .DO files to the ProjNav directory Use within the Project Navigator • VHDL • You must copy over the <project_file>.do simulation file • Testbench.vhd must be added to the .DO file • Testbench.vhd must include a configuration statement to load the RAM initialization strings included in <project_file>_init.vhd • Verilog • You must copy over the <project_file>.do simulation file • Testbench.v must be added to the .DO file • Testbench.v must include a #include statement to load the RAM initialization strings included in <project_file>_init.v

Outline • SimGen • Simulation Procedure • SmartModel Libraries

SmartModel Libraries • SmartModel Libraries are compiled simulation models that represent integrated circuits and system buses as black boxes. SmartModel Libraries: • Accept an input stimulus and respond with an appropriate output behavior • Provide improved performance over gate-level models • Protect proprietary designs • Can be used with any simulation tool that supports the SWIFT™ Interface

Running a Simulation Using SmartModels • The SWIFT™ Interface provides access to SmartModel Libraries • Changes required in the modelsim.ini • Resolution = ps • Comment out the "PathSeparator" = / using “;” • Veriuser = $MODEL_TECH/libswiftpli.dll (SWIFT Interface) • libsm = $MODEL_TECH/libsm.dll • libswift = $LMC_HOME/lib/pcnt.lib/libswift.dll • set MODELSIM=<path_to_modelsim.ini_script>\modelsim.ini • Instantiate the appropriate MGT or PowerPC primitive

Supported Simulators and Platforms • Solaris™ Operating System (2.8, 2.9) • MTI's ModelSim SE simulator (5.6E and newer) • Cadence NC-Verilog simulator • Cadence Verilog-XL simulator • Synopsys VCS simulator • Windows® 2000 (SP2) or Windows XP • MTI's ModelSim SE simulator (5.6E and newer) • Linux® (7.2) • MTI's ModelSim SE simulator (5.6E and newer)

Solution Records • 14597: 6.1i/5.2i/5.1i SmartModel/SWIFT Interface - How do I use the MGT and PPC SmartModels in NC-Verilog, Verilog-XL, and Synopsys VCS? • 14019: 6.1i/5.2i/5.1i SmartModel/SWIFT Interface - How do I use the MGT and PPC SmartModels in ModelSim? • 14181: Virtex-II Pro - What are the SWIFT Interface, Smart Model, VMC, and VhMC? What of these does Xilinx deliver? • 14596: 6.1i SmartModels - What simulators support SmartModel simulation? • 14365: Virtex-II Pro PowerPC - What is the difference between Bus Functional Model (BFM) and Smart Model (SWIFT interface) simulation?

Review Question • Which three items are required to initialize memory in the simulation models created by SimGen?

Answer • Which three items are required to initialize memory in the simulation models created by SimGen? • The compiled executable generated with the appropriate gcc compiler or assembler, from corresponding C or assembly source code • The simulation model generated by executing PlatGen and then SimGen • The BMM file generated by PlatGen

Where Can I Learn More? • Tool documentation • Getting Started with the Embedded Development Kit • Embedded System Tools Guide Simulation Models Generator • Support website • Xilinx Home Page: support.xilinx.com • EDK Home Page: support.xilinx.com/edk