Modeling with Constraint Logic Programming

Modeling with Constraint Logic Programming. Ulf Nilsson Dept of Computer and Information Science Linköping University. R. V. r(R). c(V). C1. C2. ser(C1, C2). C1. par(C1, C2). C2. Representing DC Circuits. 9V. 10. ser(c(9), par(r(10), r(5))). 5. circuit(c(N)) :- {N>=0}.

Modeling with Constraint Logic Programming

E N D

Presentation Transcript

Modeling with Constraint Logic Programming Ulf Nilsson Dept of Computer and Information Science Linköping University

R V r(R) c(V) C1 C2 ser(C1, C2) C1 par(C1, C2) C2 Representing DC Circuits

9V 10 ser(c(9), par(r(10), r(5))) 5 circuit(c(N)) :- {N>=0}. circuit(r(N)) :- {N>=0}. circuit(ser(C1, C2)) :- circuit(C1), circuit(C2). circuit(par(C1, C2)) :- circuit(C1), circuit(C2). Example

% res(C, R) % Circuit C has resistance R res(c(V), 0) :- {V>=0}. res(r(R), R) :- {R>=0}. res(ser(C1, C2), R1+R2) :- res(C1, R1), res(C2, R2). res(par(C1, C2), R1*R2/(R1+R2)) :- res(C1, R1), res(C2, R2). Resistance

Derivation < res(ser(r(X), r(X)), 10), | true > < r(X)=C1, r(X)=C2, 10=R1+R2, res(C1,R1), res(C2,R2) | true > < res(r(X),R1), res(r(X),R2) | 10=R1+R2 > < r(X)=r(R), R1=R,R>=0, res(r(X),R2) | 10=R1+R2 > < res(r(X),R2) | 10=X+R2 , X>=0 > < true | 10=X+X, X>=0 > X=5

Typical CLP program solve(Term) :- setup_constraints(Term), redundant_constraints(Term), solve_constraints.

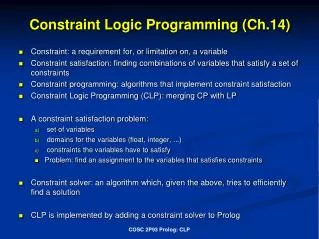

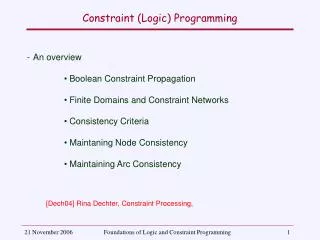

Language of CLP(B) • Boolean constants: 0 and 1 • Parameters: X, Y, ... • Negation: ~ • Binary connectives: *, +, #, =<, =:=, ... • Cardinality: card(Is, Es)

CLP built-ins • sat(BOOLEXPR)The boolean expression is added to the constraint store if the store is still satisfiable • taut(BOOLEXPR, TRUTHVAL)Succeeds if TRUTHVAL=1 and BOOLEXPR is entailed by the constraint store or if TRUTHVAL=0 and ~BOOLEXPR is entailed by the constraint store. • labeling(VARLIST)Enumerates all bindings of the variables in VARLIST that satisfy the constraint store.

Examples ?- sat(A+B), sat(~A). A=0, B=1 ?- sat(A*B), sat(~A). no ?- sat(A+B), sat(~A), taut(B, 1). A=0, B=1 ?- sat(A=:=B), labeling([A,B]). A=0, B=0 A=1, B=1

Examples: Cardinality ?- sat(A+B), sat(card ([1], [A, B])). sat(A=\= B) ?- sat(A=<B), sat(card([0-1], [A, B])). A=0

Source Source Gate Gate Drain Drain nswitch(S, D, G) :- sat(D*G =:= G*S). pswitch(S, D, G) :- sat(D* ~G =:= ~G*S). Circuit Verfication n-switch MOS p-switch MOS

Example ?- nswitch(S, D, G), labeling([S, D, G]). D = 0, G = 0, S = 0 D = 1, G = 0, S = 0 D = 0, G = 1, S = 0 D = 0, G = 0, S = 1 D = 1, G = 0, S = 1 D = 1, G = 1, S = 1

z xor(X, Y, Z) :- pswitch(Tmp,1,X), nswitch(0, Tmp, X), pswitch(Z, X, Y), nswitch(Z, Tmp, Y), nswitch(Z, Y, Tmp), pswitch(Z, Y, X). 0 tmp y x 1 1 1 Circuit verification (cont’d) 0

Is It Really an XOR? ?- xor(X, Y, Z). sat(X=:=Y#Z) ?- xor(X,Y,Z), labeling([X, Y, Z]). X = 0, Y = 0, Z = 0 X = 1, Y = 0, Z = 1 X = 1, Y = 1, Z = 0 X = 0, Y = 1, Z = 1

Testing vs Verification Can we verify the circuit without testing it? Yes! Schematically: ?- sat(System), taut(Property, 1). ?- xor(X, Y, Z), taut(Z=:=X#Y, 1). sat(X=:=Y#Z)

Property is entailed by System iff (System * ~Property) is unsatisfiable Very Useful Theorem ?- xor(X, Y, Z), sat(~(Z=:=X#Y)). no