Concurrent vs Sequential

E N D

Presentation Transcript

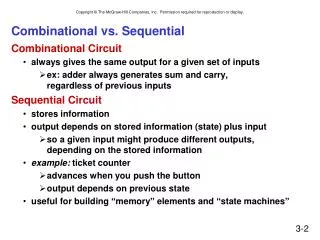

Concurrent vs Sequential • Combinational vs Sequential logic • Combinational logic is that in which the output of the circuit depends solely on the current input • Sequential logic is defined as that in which the output does depend on previous inputs. DSD,USIT,GGSIPU

Concurrent statement • Operators • The WHEN statement • (When/Else or With/select/when) • The GENERATE statement • The BLOCK statement DSD,USIT,GGSIPU

Operators • Most basic way of creating concurrent code. • Operators can be used to implement any combinational circuit. • Operators • AND, OR, +, - , * , sll, sra, etc DSD,USIT,GGSIPU

Operators DSD,USIT,GGSIPU

When (Simple and selected) • Fundamental concurrent statement • Syntax assignment WHEN condition ELSE assignment WHEN condition ELSE ……….; DSD,USIT,GGSIPU

Important Aspect of WHEN • WHEN value -- Single value • WHEN value1 to value2 – Range, for enumerated data types • WHEN value1|value2|……… - value1 or value2 DSD,USIT,GGSIPU

Circuit of 2:4 decoder DSD,USIT,GGSIPU

3:8 Decoder • entity decodedr38 is • Port ( a : in std_logic_vector(2 downto 0); • b : out std_logic_vector(7 downto 0); • en : in std_logic); • end decodedr38; • architecture Behavioral of decodedr38 is • signal temp : std_logic_vector(7 downto 0); • begin • temp <= "00000001" when a="000" else • "00000010" when a="001" else • "00000100" when a="010" else • "00001000" when a="011" else • "00010000" when a="100" else • "00100000" when a="101" else • "01000000" when a="110" else • "10000000"; • b <= temp when en='1' else • (others => '0'); • end Behavioral; DSD,USIT,GGSIPU

5x32 decoder 3:8 3:8 2:4 3:8 3:8 5:32 Decoder DSD,USIT,GGSIPU

5:32 decoder • entity decoder532 is • Port ( x : in std_logic_vector(4 downto 0); • y : out std_logic_vector(31 downto 0)); • end decoder532; • architecture Behavioral of decoder532 is • component decoder24 is • Port ( din : in std_logic_vector(1 downto 0); -- decoder input • dout : out std_logic_vector(3 downto 0) • );-- decoder output • end component decoder24; • component decodedr38 is • Port ( a : in std_logic_vector(2 downto 0); • b : out std_logic_vector(7 downto 0); • en : in std_logic); • end component decodedr38; • signal temp : std_logic_vector(3 downto 0); DSD,USIT,GGSIPU

5:32 decoder (cont..) • begin • u1: decoder24 port map(din(1)=>x(4),din(0)=>x(3),dout(3)=>temp(3),dout(2)=>temp(2),dout(1)=>temp(1),dout(0)=>temp(0)); • u2: decodedr38 port map(en=>temp(0),a(2)=>x(2),a(1)=>x(1),a(0)=>x(0),b(7)=>y(7),b(6)=>y(6),b(5)=>y(5),b(4)=>y(4),b(3)=>y(3),b(2)=>y(2),b(1)=>y(1),b(0)=>y(0)); • u3: decodedr38 port map(en=>temp(1),a(2)=>x(2),a(1)=>x(1),a(0)=>x(0),b(7)=>y(15),b(6)=>y(14),b(5)=>y(13),b(4)=>y(12),b(3)=>y(11),b(2)=>y(10),b(1)=>y(9),b(0)=>y(8)); • u4: decodedr38 port map(en=>temp(2),a(2)=>x(2),a(1)=>x(1),a(0)=>x(0),b(7)=>y(23),b(6)=>y(22),b(5)=>y(21),b(4)=>y(20),b(3)=>y(19),b(2)=>y(18),b(1)=>y(17),b(0)=>y(16)); • u5: decodedr38 port map(en=>temp(3),a(2)=>x(2),a(1)=>x(1),a(0)=>x(0),b(7)=>y(31),b(6)=>y(30),b(5)=>y(29),b(4)=>y(28),b(3)=>y(27),b(2)=>y(26),b(1)=>y(25),b(0)=>y(24)); • end Behavioral; DSD,USIT,GGSIPU

Conditional Signal Assignment statement • The conditional signal assignment statement selects different values for the target signal based on the specified, possibly different, conditions. A typical syntax – target-signal <= [waveform-elements when condition else [waveform-elements when condition else .. Waveform-elements when condition]; DSD,USIT,GGSIPU

Example 4: 1 Mux using when statement library ieee; use ieee.std_logic_1164.all; entity mux4_1_when is port (a: in std_logic_vector(3 downto 0); s: in std_logic_vector(1 downto 0); y: out std_logic ); end mux4_1_when; architecture mux_behave of mux4_1_when is begin y <= a(0) when s = "00" else a(1) when s = "01" else a(2) when s = "10" else a(3); end mux_behave; DSD,USIT,GGSIPU

Symbol of 2:1 Mux DSD,USIT,GGSIPU

Selected signal Assignment statement • The selected signal assignment statement selects different values for a target signal based on the value of a select expression. • A typical syntax – With expression select target-signal <= waveform-element when choices, waveform-element when choices,.. waveform-element when choices; DSD,USIT,GGSIPU

Example 4:1 mux using with-select library ieee; use ieee.std_logic_1164.all; entity mux4_1_with is port (a: in std_logic_vector(3 downto 0); s: in std_logic_vector(1 downto 0); y: out std_logic ); end mux4_1_with; architecture mux_behave of mux4_1_with is begin with s select y <= a(0) when "00", a(1) when "01", a(2) when "10", a(3) when others; end mux_behave; DSD,USIT,GGSIPU

Mux architecture DSD,USIT,GGSIPU

Circuit of Encoder DSD,USIT,GGSIPU

Truth table of encoder DSD,USIT,GGSIPU

7-segment display DSD,USIT,GGSIPU

Input Output No. X3 X2 X1 X0 G F E D C B A 0 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 1 0 0 0 0 1 1 0 2 0 0 1 0 1 0 1 1 0 1 1 3 0 0 1 1 1 0 0 1 1 1 1 4 0 1 0 0 1 1 0 0 1 1 0 5 0 1 0 1 1 1 0 1 1 0 1 6 0 1 1 0 1 1 1 1 1 0 0 7 0 1 1 1 0 0 0 0 1 1 1 8 1 0 0 0 1 1 1 1 1 1 1 9 1 0 0 1 1 1 0 0 1 1 1 Truth table of 7-segment display decoder DSD,USIT,GGSIPU