Fast Logic Restructuring Using Node Merging and Node Addition and Removal

Fast Logic Restructuring Using Node Merging and Node Addition and Removal . Yung- Chih Chen 陳勇志 Department of Electrical Engineering Chung Yuan Christian University. Outline. Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares

Fast Logic Restructuring Using Node Merging and Node Addition and Removal

E N D

Presentation Transcript

Fast Logic Restructuring Using Node Merging andNode Addition and Removal Yung-Chih Chen 陳勇志 Department of Electrical Engineering Chung Yuan Christian University

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

Introduction A A B B Circuit size reduction • Node merging is a logic restructuring technique • Replace one node with another node in a logic circuit

Introduction • Two nodes can be correctly merged when • they are functionally equivalent, or • their functional differences are never observed at a primary output (PO) • Observability Don’t Care (ODC)

Example • And-Inverter Graph (AIG) n6and n8are not functionally equivalent Their values only differ when x3 = 1and x2 = x4 x2 = x4implies n7= 0, n7= 0 blocks n8 The functional differences of n6and n8are never observable n8can be replaced with n6 x1 n12 n1 n5 n9 x2 n2 n6 n10 n13 1 x3 n3 0 n7 n11 x4 1 n4 n8 5

Problem formulation • Given a target node nt, find other nodes called substitute nodes which can replace nt without changing the circuit’s functionality • Inputs: a circuit and a target node • Outputs: substitute nodes

Previous works ODC computation SAT solving Full observability computation is VERY expensive Satisfiability (SAT)-based methods

Previous works [1] Q. Zhu, N. Kitchen, A. Kuehlmann, and A. Sangiovanni-Vincentelli, “SAT Sweeping with Local Observability Don’t Cares,” in Proc. Design Automation Conf., 2006, pp. 229-234. [2] S. Plaza, K. H. Chang, I. Markov, and V. Bertacco, “Node Mergers in the Presence of Don’t Cares,” in Proc. Asia South Pacific Design Automation Conf., 2007, pp. 414-419. • Local ODC computation [1] • Compute local ODC within a bounded-depth k • A node is observable when it is observable at the bounded-depth k • CPU time: controllable • Capability: exact when kis ∞, limited to k • Global ODC computation [2] • Compute global but approximate ODC • CPU time: time-consuming • Capability: not limited to local ODC but not exact

Our method • One sufficient condition for safely merging two nodes • ATPG-based approach • NO random simulation, NO ODC computation, NO candidates, and NO SAT solving • Run time: efficient • Also find functional equivalent and global ODC-based mergers • Capability: competitive

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

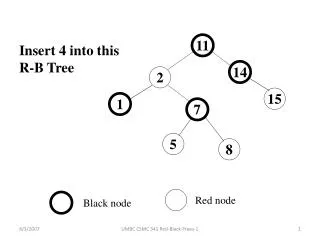

Stuck-at fault test stuck-at 0 1 1 1 1 n 0 n 1 1 1 1 • A stuck-at fault test • A process to find a test vector which generates different values in the fault-free and faulty circuit • A test vector exists → testable; otherwise, untestable • A test vector must activate and propagate the fault effect to a PO • generates n = 1 • propagates n = 1to a PO

Mandatory assignment (MA) x2 Consider n8’s stuck-at 0 fault: n2 n6 x3 n3 n7 n8=1, n4=0, n3=1, n7=1, n2=1, n6=1 are MAs n11 x4 n4 n8 stuck-at 0 • Given a stuck-at fault, MAs are • unique value assignments to nodes required for a test vector to exist • MAsare necessary for detecting a stuck-at fault

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

Node merging and misplaced wire error w1 w1 w2 w2 nt nt w3 w3 ns ns Correct circuit C Incorrect circuit C’ • Replacing nt with ns can be considered a misplaced wire error • The wires, w1 ~ w3, should be connected with nt instead of ns

A test vector of a replacement error detectsnt’s stuck-at0 fault and generates ns = 0 ns = 1 is necessary for detectingnt’s stuck-at 0 fault nt nt detectsnt’s stuck-at1 fault and generates ns = 1 ns = 0 is necessary for detectingnt’s stuck-at 1 fault ns ns • To detect a replacement error, a test vector must • 1) generates nt≠ns, and • generates nt = 1 and ns = 0, or • generates nt = 0 and ns = 1 • 2) propagates the value of nt to a PO

A sufficient condition ns = 1 is necessary for detectingnt’s stuck-at 0 fault, and ns = 1 is an MA of nt’s stuck-at 0 fault, and ns = 0 is necessary for detectingnt’s stuck-at 1 fault ns = 0 is an MA of nt’s stuck-at 1 fault ns = 0 is an MA of nt’s stuck-at 0 fault, and ns = 1 is an MA of nt’s stuck-at 1 fault • Condition: • ntcan be replaced with ns • No test vector can generatent≠ns,and propagate the value of nt to a PO simultaneously • ntcan be replaced with INV(ns)

Example n12 x1 n1 n5 n9 x2 n2 n6 n10 n13 x3 n3 n7 n11 x4 n4 n8 MAs(n8=sa0):{n8=1, n4=0, n3=1, n7=1, n2=1, n6=1} MAs(n8=sa1):{n8=0, n7=1, n4=0, n2=1, n3=0, n6=0, n10=0} Substitute nodes: n6, n3

Substitute node identification MAs(nt=sa0) MAs(nt=sa1) ns • Two MA computations are required for each node • MAs(nt=sa0) andMAs(nt=sa1) • It could identify more than one substitute node

Experimental setup [3] Berkeley Logic Synthesis and Verification Group, “ABC: A System for Sequential Synthesis and Verification,” http://www.eecs.berkeley.edu/alanmi/abc/. • Within ABC [3] environment and on a Linux platform (CentOS 4.6) with a 3.0GHz CPU • Two experiments • Substitute node identification • Circuit size reduction • Each benchmark is initially optimized by using resyn2, a local rewriting optimization

Circuit size reduction (1/2) [2] S. Plaza, K. H. Chang, I. Markov, and V. Bertacco, “Node Mergers in the Presence of Don’t Cares,” in Proc. Asia South Pacific Design Automation Conf., 2007, pp. 414-419.

Summary • Yung-Chih Chen, Chun-Yao Wang, "Fast Detection of Node Mergers Using Logic Implications", 2009 IEEE/ACM International Conference on Computer-Aided Design (ICCAD2009), pp. 785-788, Nov. 2009. • Yung-Chih Chen, Chun-Yao Wang, "Fast Node Merging with Don’t Cares Using Logic Implications", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, pp. 1827-1832, Nov. 2010 • We propose a fast ODC-based node merging algorithm • ATPG-based • 3.3 substitute nodes • 46.81x faster • We propose a node merging-based approach for circuit size reduction

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

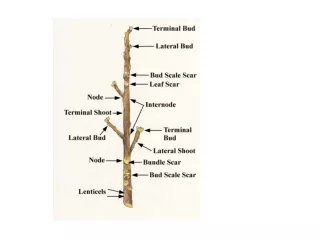

Node addition and removal A A A B B B C Node addition and removal (NAR) is an extended technique of node merging

Example: node merging and NAR And-Inverter Graph (AIG) n5and n6are functionally non-equivalent Their values only differ when n2 = 1 and a = c a = c implies n1 = 0, whichblocks n5 The functional differences of n5 andn6are never observable n5can be replaced with n6 n7 n1 a n5 n6 b n2 n3 c n4 d

Example: node merging and NAR And-Inverter Graph (AIG) There is no substitute node that can replace n6 The added node n8 can replace n6 n2 can be removed as well n7 n1 a n6 b n2 n3 c n8 n4 d NAR can complement node merging

Problem formulation Given a target node ntin a circuit, find a node nawhich can safely replace ntafter it is added into the circuit na is named anadded substitute node and driven by two nodes existing in the circuit

Node addition and removal Extend our prior node-merging method sufficient conditions for an added node to be an added substitute node NAR and node merging both perform node replacement If an added node na satisfies Condition 1, it is a substitute node, and thus, an added substitute node na=1 in MAs(nt=sa0) na=0 in MAs(nt=sa1) 29

Node addition and removal ? n7 n1 a ? ? n6 b n2 ? ? n3 c n4 d ? We do not iteratively add any one node and then check if it is an added substitute node due to inefficiency

Node addition and removal Identify two existing nodes, nf1andnf2,which are fanin nodes of an added substitute node na Suppose na = AND(nf1, nf2) na=1 in MAs(nt=sa0) na=0 in MAs(nt=sa1) {nf1=1, nf2=1} in MAs(nt=sa0) nf2=0 in imp({nf1=1, MAs(nt=sa1)}) nf1 na nf2

Experimental setup Within ABC environment and on a Linux platform (CentOS 4.6) with a 3.0GHz CPU Three experiments Replaceable node identification Circuit minimization Each benchmark is initially optimized by using resyn2, a local rewriting optimization

Circuit minimization • Average results for totally 23 benchmarks • Combine our approach with resyn2

Summary We proposed an ATPG-based NAR approach No random simulation, no candidates, and no SAT solving Complement the node-merging approach by finding more replaceable nodes It has a competitive quality and spends much less CPU time, compared to the SAT-based node-merging approach • Yung-Chih Chen, Chun-Yao Wang, "Node Addition and Removal in the Presence of Don’t Cares", 2010 ACM/IEEE Design Automation Conference (DAC2010), pp. 505-510, July 2010. (Best Paper Nominee) • Yung-Chih Chen, Chun-Yao Wang, "Logic Restructuring Using Node Addition and Removal", accepted by IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

SAT-based bounded sequential equivalence checking SAT-based BSEC PIs PIs PIs PIs F0 F1 Fn-1 Fn S0 . . . G0 G1 Gn-1 Gn POs POs POs POs . . . T=0 T=1 T=n-1 T=n

Optimization flow SAT-based bounded sequential equivalence checking Miter Unrolling PIs PIs PIs F’n F0 F’0 FFs NM & NAR . . . FFs G’n G0 G’0 POs POs POs SAT solving NM & NAR

SAT-based BSEC facilitation • Yung-Chih Chen, Chun-Yao Wang, "Logic Restructuring Using Node Addition and Removal", accepted by IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

Outline Introduction Preliminaries Node merging with don’t cares Node addition and removal with don’t cares Satisfiability-based bounded sequential equivalence checking Conclusion

Conclusion • We propose two logic optimization methods • ATPG-based node merging • Faster than previous SAT-based methods • Competitive quality • ATPG-based node addition and removal • Enhance node merging • They can be integrated to facilitate SAT-based BSEC