Static Memory

Outline Types of Static Memory Static RAM Battery Backup EPROM Flash Memory EEPROM Goal Understand types of static memory Understand static memory design Reading Microprocessor Systems Design, Clements, Ch. 5.3. Static Memory. Terminology static - maintains state without any action

Static Memory

E N D

Presentation Transcript

Outline Types of Static Memory Static RAM Battery Backup EPROM Flash Memory EEPROM Goal Understand types of static memory Understand static memory design Reading Microprocessor Systems Design, Clements, Ch. 5.3 Static Memory

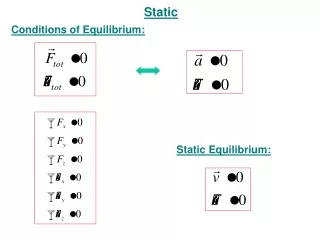

Terminology static - maintains state without any action nonvolatile - maintains state without power solid-state - semiconductor, not disk, tape, etc. Memory types SRAM - static read/write random access memory ROM - nonvolatile read only memory EPROM - fast read, off-line chip erase/write ROM Flash - fast read, slow block erase/write ROM EEPROM - fast read, slow byte erase/write ROM Types of Static Memory

Static read/write random access memory CPU can quickly read and write each memory location CPU can access each memory location at same speed fastest type of memory use for small amount of RAM low power consumption when idle can use battery backup SRAM cell 6 transistor (6T) cell 4 transistor and 2 resistor (4T) cell Static RAM Sel Sel B B* B B*

1, 4, 8, 16, 24, 32-bits wide width to match chip count for memory capacity Pin compatibility SRAM parts have corresponding ROM, EPROM, etc. Bus contention memories A and B both putting data on bus memory and CPU both putting data on bus SRAM Configuration

Bus Contention Data bus D00-D31 <D00:D15> <D16:D31> 4Mx16 4Mx16 <D0:D15> <D0:D15> <A0:A21> CS* R/W* <A0:A21> CS* R/W* Address bus A00-A31 Two 4Mx16 SRAMs form one 4Mx32 memory bank

CSA* and CSB* must make sure A and B don’t drive the bus at the same time bus contention or fight with CPU or other device address decoder timing issue SRAM Configuration Data bus D00-D31 4Mx32 4Mx32 A B <A0:A21> CS* R/W* <A0:A21> CS* R/W* CSA* CSB* Address bus A00-A31

CMOS SRAM uses little power while idle can be placed in special power-down mode < 50 uA for 6264LP-10 chip battery can supply power save state when power is off - e.g. setup parameters selecting powerdown deselect chip, drop supply voltage Battery approach rechargeable NiCad 1.2V cell, put in series for higher voltage charge off power supply drawback - self-discharge of 1%/day at 15C, 8%/day at 50C can only use for short-term power loss Battery Backup

Diode isolated diode blocks power supply when it goes away resistor in series with battery limits charging current C/10 where C = capacity in A-h 0.1 A-h battery => 10 mA charging current Vdd = 5V, 2.4V battery => 260 ohm resistor causes 13 mV voltage drop at 50 µA draw also have diode leakage Problem Vdd of 6264 SRAM is 4.3-4.6V Vdd of 68K is 5V could overdrive SRAM inputs, cause latchup solution - pass CPU Vdd through diode better - use transistor cutoff Backup Supply Design TTL Vcc 5V CMOS Vcc Rc

Must have chip inputs at Vdd or GND otherwise they can draw large power Solution use open-collector drivers with pullup resistors connect resistors to battery supply easier to use active low chip select otherwise must guarantee select is low but drivers are another source of leakage current Chip select tie to battery supply - falls when battery takes over use supply comparator - deselect when battery > Vdd Chip Inputs

Erasable, programmable ROM use when data infrequently changed e.g. PostScript interpreter in printer EPROM cell floating FET gate, stores charge 12-25V on select gate injects charge into floating gate done on special PROM programmer complex programming cycle erase with bright UV light - all gates to 0V chip has quartz window EPROM usage similar to read cycle in SRAM EPROM Vgate +N N+ P-

Flash electrically erasable PROM program similar to EPROM erase with Fowler-Nordheim tunneling 12-20V across thin ONO oxide electrons tunnel through it at S/D to erase Bulk erase flash erases whole chip or block/sector at a time slow - can take 100 ms to 1 s Erase/program in system chip has internal voltage generator and program/erase logic not like in book Limited lifetime limited to 10K-100K erase/program cycles - oxide wears out Usage - solid state disk, BIOS, embedded OS, etc. cheaper than battery-backed SRAM Flash Memory

Electrically-erasable PROM erase/program with tunneling faster erase, slower programming than flash Byte erase/program automatically erase before program looks like a slow SRAM on-chip voltage generator and timing CPU can poll chip to see if write is done Buffering many EEPROMs have SRAM buffer CPU can do series of quick writes, which are then stored Intelligence put chip into read-only mode erase entire chip and disable auto-erase EEPROM