ECSE-6230 Semiconductor Devices and Models I Lecture 12

280 likes | 732 Vues

ECSE-6230 Semiconductor Devices and Models I Lecture 12. Prof. Shayla Sawyer Bldg. CII, Rooms 8225 Rensselaer Polytechnic Institute Troy, NY 12180-3590 Tel. (518)276-2164 Fax. (518)276-2990 e-mail: sawyes@rpi.edu. April 2, 2014. sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html . 1.

ECSE-6230 Semiconductor Devices and Models I Lecture 12

E N D

Presentation Transcript

ECSE-6230Semiconductor Devices and Models ILecture 12 Prof. Shayla Sawyer Bldg. CII, Rooms 8225 Rensselaer Polytechnic Institute Troy, NY 12180-3590 Tel. (518)276-2164 Fax. (518)276-2990 e-mail: sawyes@rpi.edu April 2, 2014 sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html 1

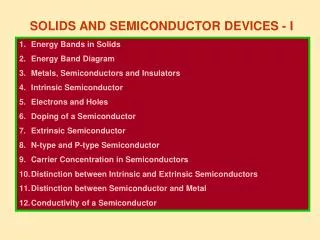

Lecture Outline Qs vs. s (review of terms) Ideal MIS Capacitance Curves Low frequency High frequency MOS Capacitors Interface charges Metal-Semiconductor Work Function Difference Oxide Charges (Threshold voltage)

Surface Potential Potential, ψ, defined at any point x relative to the equilibrium position of Ei(x)/q (extent of band bending at x) ψs is band bending at x=0 surface potential Ψs = 0 flat band condition Ψs < 0 bands bend up (accumulation) Ψs > 0 bands bend down (depletion) Ψs = 0 and larger than ΨBp (inversion obtained) Strong inversion, Ψs is twice the value of ΨBp sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html

Surface Potential Potential, ψ, defined at any point x relative to the equilibrium position of Ei(x)/q (extent of band bending at x) ψs is band bending at x=0 surface potential Ψs = 0 flat band condition Ψs < 0 bands bend up (accumulation) Ψs > 0 bands bend down (depletion) Ψs = 0 and larger than ΨBp (inversion obtained) Strong inversion, Ψs is twice the value of ΨBp sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html

Surface Potential Electron and hole concentrations as a function of ψ (ψp) are given by: Integrate from surface to the bulk to get electric field sawyes@rpi.edu www.rpi.edu/~sawyes/courses.html

Qs vs. s • Accumulation first term in dominant where surface potential is negative • Depletion second linear term is dominant • Ratio of minority to majority carrier concentration is very small • With enough band bending (2ψBp) the second exponential term due to ratio is dominant (Strong inversion) Strong inversion Depletion/ Weak inversion accumulation

Strong Inversion and Capacitance Strong inversion Charge neutrality states Total capacitance is the series combination of the insulator capacitance and depletion layer capacitance

Strong Inversion Voltage drop: insulator and semiconductor CD depends on bias (or ψs) and also a function of measurement frequency

Ideal MIS Capacitance Voltage applied to the metal relative to the p-semiconductor -V is accumulation (basically parallel plate insulator capacitance) Reaches flat band (V=0 is assumed) Capacitance dependence with frequency a) low b) intermediate c) high d) high with fast sweep (deep depletion)

Low Frequency Capacitance Semiconductor CD is obtained by differentiating the total static charge in semiconductor size with respect to surface potential Slope in Qs vs. ψsfigure Total Capacitance at flatband

Low Frequency Capacitance Under depletion and weak inversion the function in the denominator reduces to Space charge density can be reduced to Express depletion width as a function of terminal voltages With WD, CD and ψs are deduced Capacitance continues to decrease until an inversion layer forms at the surface

Low Frequency Capacitance At low frequencies the recombination-generation rates of minority carriers can keep up with small signal variation Leads to charge exchange with the inversion layer in step with the measurement signal Incremental charge at the semiconductor is now at the semiconductor surface inversion layer resulting in a large capacitance

High Frequency Capacitance High frequency curve is obtained using an approach analogous to a one sided pn junction Ionized acceptor in the depletion region given by –qNAWD where WD is the depletion width Integrating Poisson’s equation yields the potential distribution in the depletion region: Where the surface potential is given by

High Frequency Capacitance Applied voltage increases, Ψs and WD increase until strong inversion WDm reaches a maximum The semiconductor is effectively shielded from further penetration of the electric field by the inversion layer Small increase in band being means large increase in inversion charge layer

High Frequency Capacitance Small signal is too fast for minority carriers and the incremental charge is put at the edge of the depletion region Depletion capacitance is given by εi/WD with a minimum value corresponding to the maximum depletion width

Ideal Threshold Voltage Instead of more depletion (maximum WDm) strong inversion occurs. The threshold voltage required for strong inversion is We assume that Ψs = 0 when VG = 0

MOS Capacitors For a practical MOS capacitor, interface traps and oxide charges exist and will affect the ideal MOS characteristics (strongly affect VT and other properties) Work function difference between the metal or doped polysilicon gate and substrate, depends on substrate doping (here polysilicon acts as a metal electrode) Inevitably, there are charges at the Si-SiO2 interface and within the oxide that must be taken into account

Flatband Voltage Factors influencing the flatband voltage in MOS system: Metal-Semiconductor Work Function Difference ms = m - s where q s = q + Eg / 2 + q B With Al or poly-Si as the gate electrode, ms < 0 and the semiconductor bands bend downwards ms ( n+ poly-Si gate over p-type Si ) = F ( n+ poly-Si gate) - F ( semiconductor) = Eg / 2 - ( kT/q) ln ( NA / ni ) ( reference to Ei ) where EF EC for the heavily doped n+ poly-Si, the effective work function is equal to the Si electron affinity (ΧSi = 4.05V)

ms • An advantage of a polysilicon gate: The same material can give different work functions by doping.

Oxide and Interface Charges Interface traps of density Dit and trapped charges Qit, located at the Si-SiO2 interface with energy states within the silicon forbidden gap Bias dependent (occupancy and Fermi level) Fixed oxide charges Qf, located at or near the surface, immobile under an applied electric field Oxide trapped charges, Qot, created by X-ray radiation or hot electron injection Mobile ionic charges, Qm, sodium ions are mobile within the oxide under bias temperature stress conditions

Oxide and Interface Charges The flat band voltage shift due to any oxide charge is given by Gauss’s law Effect of voltage shift is weighted according to the location of the charge The closer to the oxide-semiconductor interface, the more shift it will cause

Oxide and Interface Charges Fixed oxide charges Depends on oxidation and annealing conditions Generally positive and located very close to Si-SiO2 interface Mobile ionic charge Moves back and forth through the oxide depending on biasing conditions Enhanced at elevated temperature Mainly responsible for instability of oxide passivated devices Oxide trapped charge Usually initially neutral and are charged by introducing electrons and holes in the oxide layer Caused by current passing through oxide layer, hot carrier injection or photon excitation

Example Problem An n+ - polysilicon gate n-channel MOS transistor is made on a p-type Si substrate with Na=5 x 1015 cm-3. The SiO2 thickness is 100 Å in the gate region, and the effective interface charge Qi is 4 x 1010 qC/cm2 . Find Ci and Cmin on the C-V characteristic, and find Wm, VFB, and VT.