ALTERNATIVE SMALL-SIGNAL BIPOLAR TRANSISTOR

410 likes | 991 Vues

ALTERNATIVE SMALL-SIGNAL BIPOLAR TRANSISTOR. Introduction (1/2). Originally, it was the development of the standard bipolar NPN and substrate lateral PNP transistors Process extensions:

ALTERNATIVE SMALL-SIGNAL BIPOLAR TRANSISTOR

E N D

Presentation Transcript

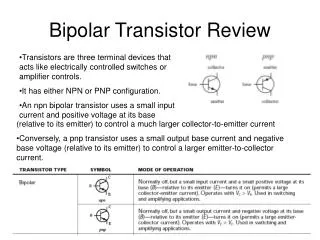

Introduction(1/2) • Originally, it was the development of the standard bipolar NPN and substrate lateral PNP transistors • Process extensions: allows standard bipolar to fabricate NPN transistors with extremely high betas and lateral PNP transistors with improved high-current performance

Introduction(2/2) • Analog BiCMOS: -offers bipolar transistors with reduced feature sizes that can equal or even surpass the performance of standard bipolar • Advanced bipolar and BiCMOS: -offer extremely high-speed transistors suitable for fast digital logic • These advanced transistors are also useful for constructing ultra-fast amplifiers and comparators

Extensions to standard bipolar • Standard bipolar was perfected in the 60s • Many other processes have been developed since then that offer superior device performance, but most of them have proven to be too costly or too complex to justify their widespread adoption • Two options that have enjoyed some measure of popularity are the super-beta NPN and the deep-P+ lateral PNP • Only real advantages of standard bipolar are its simplicity and its low cost

Super-beta NPN(1/2) • Employs a deeper emitter diffusion that decreases the width of the neutral base to less than 0.1um, which allows Betas in excess of 5000 are possible • The thin, lightly doped base punches through at collector-to-emitter voltages of only 1 to 3V, and early voltages lie in the same range, these limitations restrict super-beta transistors to a few specialized applications • Alternatives like BiFET and BiCMOS can replace super-beta transistors, but it ramains cost saving to use super-beta transistors in older products

Super-beta NPN(2/2) • Comparison of cross sections of standard bipolar NPN and a super-beta NPN

Deep-P+ lateral PNP(1/2) • Employs a special deep-P+ diffusion that is more heavily doped and deeper than the regular base diffusion • The increase in dopant concentration improves the emitter injection efficiency • The deeper junction ensures that a larger percentage of emitter injection occurs from the sidewalls • Deep-P+ laterals can operate at current densities two or three times as large as base laterals

Deep-P+ lateral PNP(2/2) • Comparison of cross sections of a standard bipolar lateral PNP and a deep-P+ lateral PNP

Analog BiCMOS Bipolar Transistors(1/8) • Analog BiCMOS process employs a P-type9(100) epi instead of the N-type(111) epi favored by standard bipolar • Components must occupy N-wells isolated from one another by regions of P-epi • Except for the substitution of N-wells for N-tanks, the construction of bipolar devices in analog BiCMOS parallels that in standard bipolar

Analog BiCMOS Bipolar Transistors(2/8) • Difficulties of using N-well to form the collector of the NPN(CDI NPN): -the nature of the well causes the resistivity of its lowest portions to greatly exceed the resistivity of standard bipolar N-epi -the vertical resistance through the N-well is much greater than the vertical resistance through the standard bipolar N-epi -without deep-N+ sinker, the vertical collector resistance will cause a soft transition from saturation to normal active operation -shallow junction depth of N-well limits the operating voltage to 15 to 20V

Analog BiCMOS Bipolar Transistors(3/8) • Comparison of saturation characteristics of CDI NPN transistors with and without the addition of deep N+ sinker

Analog BiCMOS Bipolar Transistors(4/8) • Extended-base transistor: -does not employ N-well in its construction -base consists of the base diffusion and an isolated P-epi region -a ring of deep-N+ isolates the base from the surrounding P-epi, which also allows contact to the NBL -collector consists of the NBL beneath its extended base and the deep-N+ ring surrounding it the extended base structure has a higher planar base-collector breakdown voltage then the CDI NPN, resulting in a higher Vceo ranging from 40 to 60V

Analog BiCMOS Bipolar Transistors(5/8) • Layout and cross section of an extended-base NPN transistor

Analog BiCMOS Bipolar Transistors(6/8) • If the base diffusion was eliminated: -it will form the epi-base transistor -resulting in a reduced Gummel number -epi-base transistor offers a high beta at the cost of reduced operating voltage and increased base resistance -epi-base transistor does not require a separate base diffusion

Analog BiCMOS Bipolar Transistors(7/8) • Analog BiCMOS substrate PNP: -employs an emitter constructed of PSD rather then base -larger junction depth of the base diffusion reduces the punchthrough voltage of the transistor -substrate PNP transistors inject current into the substrate, the designer must take precautions to avoid substrate biasing

Analog BiCMOS Bipolar Transistors(8/8) • Lateral PNP transistors: -exhibits high peak betas -relative shallowness of the base diffusion allows the emitter n collector to be placed in close proximity to one another and the graded nature of the well helps increase the punchthrough voltage near the surface where the base is narrowest

Bipolar Transistors in a CMOS Process (1/7) We can produce substrate PNP using N-well CMOS process. Similarities between the substrate PNP and BiCMOS: Emitter from PSD, Base from N-well, Collector from P-substrate Performance is less than that of a BiCMOS device: Difference in N-well doping Use of shallow clad moats

Bipolar Transistors in a CMOS Process (2/7) • N-well doping: • In CDI NPN: lightly doped, acts as the drift region. • In lateral & substrate PNP: acts as the base region. • In High voltage long channel PNP transistors it forms a backgate. • In modern CMOS process: Channel length is less than 1 micron • We use higher doping of the well to prevent punchthrough • Draw back: reducing the gain of the substrate PNP

Bipolar Transistors in a CMOS Process (3/7) • MOS structure: • Thin S/D implants in short channel MOS trans. Reduces emitter injection efficiency • Bad idea to use clad moat in silicidation process as silicidation consumes the silicon layer in the S/D implants and therefore thins the already thin S/D diffusion.

Bipolar Transistors in a CMOS Process (4/7) • The gain of the PNP transistor vary from less than 1 to more than 50. • Variations in Beta β produce variations in base current. • Collector current mismatches of 3 to 5% are common in low gain CMOS substrate transistors. • Even though this variation is small, it becomes more obvious when Beta β reaches unity.

Bipolar Transistors in a CMOS Process (5/7) • Layout of Substrate PNP transistors in N-well CMOS process: • Silicide block mask is coded over the emitter region. • Minimum width NSD and PSD strips are interchanged, thus reducing the resistance of the base of the transistor and help reduces base current variation in matching process

Bipolar Transistors in a CMOS Process (6/7) There has been attempts to construct lateral PNP transistors in straight CMOS processes. These were proved to be unsuccessful because of low gain, low collector efficiency, and a value of Beta reaching unity which prevents matching processes. A solution is to use Polysilicon to construct the base region Drawback: large variation in Beta still exist

Bipolar Transistors in a CMOS Process (7/7) • An alternative to lateral PNP transistors can be fabricated by the presence of the NBL. • The resulting transistor can not handle high currents as a result of high resistivity collectors, but they show better performance than other CMOS process devices

Advanced-technology Bipolar Transistors • Limits on switching speeds • Junction capacitance • Base resistance • Neutral base width • Switching transistors • Transit time limitations

Washed-emitter Transistor • Simplest way to educe junction capacitance? • Smaller geometries using improved photolithography

Polysilicon Emitter Transistors • Deposition of arsenic-doped polysilicon • Thin and heavily doped emitter diffusion • Betas of six or more times greater

Did you know? • Polysilicon emitters are universally used in BiCMOS technologies as part of the silicon bipolar transistors or SiGe heterojunction bipolar transistors. Polysilicon emitters have a number of important advantages: • Improved gain. • Scalability to deep sub-micron geometries. • Can be used in self-aligned fabrication schemes that minimise parasitic capacitance and resistance • Compatibility with CMOS.

Partial Oxide Isolation • LOCOS prosses to oxidize • Less collector substrate capacitance • Shrinks tank dimensions • Listen and write this down

Polysilicon Emitter Transistors (Contd.) • Increased emitter junction efficiency • Grain boundaries in the polysilicon • Thin interfacial oxide • Heavily doped base region • Precise emitter junctions • Conclusion

Super Self-aligned (SSA) Structure • Dual or hybrid • Base and emitter use doped polysilicon • 250ps (WHOAA that’s fast!) • Complexity limits application