Data Strobe (DS) Encoding Sam Stratton sam.stratton@aeroflex.com

Data Strobe (DS) Encoding Sam Stratton sam.stratton@aeroflex.com. 2006 MAPLD International Conference Washington, D.C. September 25, 2006. DS Encoding. Strobe signal is sent along with the serial Data The clock is extracted by XORing the Data and Strobe signals. Pros and Cons. Pros

Data Strobe (DS) Encoding Sam Stratton sam.stratton@aeroflex.com

E N D

Presentation Transcript

Data Strobe (DS) EncodingSam Strattonsam.stratton@aeroflex.com 2006 MAPLD International Conference Washington, D.C. September 25, 2006

DS Encoding • Strobe signal is sent along with the serial Data • The clock is extracted by XORing the Data and Strobe signals

Pros and Cons • Pros • Nearly 1 bit time of skew Margin • Good Jitter Tolerance • Cons • Receiver data is asynchronous with respect to local clocks

Implementation Challenges • Receiver for decode of Data Strobe waveforms is an asynchronous circuit • Analyze asynchronous circuit to guarantee no race conditions violate timing • Implementation of asynchronous circuits are difficult in FPGAs • FPGA vendors do not guarantee minimum timing of parts • Routing variations for common circuit • Interconnect delay variances • ASIC designs can more easily guarantee minimum timing of circuits

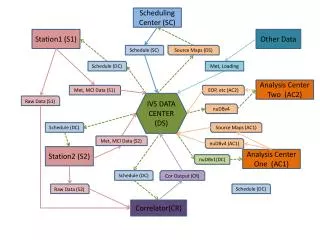

DATA path delay DATA D D Q Q D D Q Q FF0 FF2 I_3 CLK_BUFF CLK_BUFF XOR XOR STROBE D D Q Q D D Q Q FF1 FF3 DS Circuit Analysis • Only first 2 Flip Flips (FFs) are asynchronous • FF0 & FF1 • All other FFs in shift register are synchronous with single clock edge • Timing Checks • Setup • Data changing • Hold • Strobe changing • Minimum pulse width • Conditions • Data changing • Strobe changing

Timing ChecksSet-up Time • Setup Checks • Ensure Data that generated the clock arrives before the clock • Blue is faster than Red • T(Data to FF[D]) <T(Data to FF[Clk])-T(Set-up FF) • For FPGA - use longest path and shortest path together for worst case • Consider rising and falling edge permutations DATA path delay DATA D D Q Q D D Q Q FF0 FF2 I_3 CLK_BUFF CLK_BUFF XOR XOR STROBE D D Q Q D D Q Q FF1 FF3

Longer Bit Period Data skew Strobe skew Bit Period Clock Shorter Bit Period Timing ChecksHold Time • Hold Checks • Ensure Strobe generated clock does not latch the wrong Data • Red shorter than Bit Period (T) of Data rate • Note Bit Period defined from rising to falling edge • TBit Period +T(Data to FF[D]) >T(Strobe to FF[Clk])+T(Hold FF) • For FPGA - use longest path and shortest path together for worst case • Consider rising and falling edge permutations DATA path delay DATA D D Q Q D D Q Q FF0 I_3 FF2 CLK_BUFF CLK_BUFF XOR XOR STROBE D D Q Q D D Q Q FF1 FF3

Timing ChecksMinimum Edge Separation • Min Edge Separation Checks • Ensure Bit Period is greater than Absolute value of difference in Data clock generated path delay and Strobe clock generated path delay • TMin Bit Period >|T(Strobe to FF[Clk])-T(Data to FF[Clk])| + T(Set-up) + T(Hold) • For FPGA - use longest path and shortest path together for worst case • Consider rising and falling edge permutations DATA path delay DATA D D Q Q D D Q Q FF0 FF2 I_3 CLK_BUFF CLK_BUFF XOR XOR STROBE D D Q Q D D Q Q FF1 FF3

ASIC vs FPGA • Traces are the primary contributor to delays • ASIC • - Critical paths can be carefully managed • FPGA • - Path lengths cannot be changed, only links to paths FPGA, Fixed Architecture ASIC, No Fixed Architecture

Summary • DS Encoding offers good Skew and jitter margins • Better suited for ASIC Implementations • FPGA Implementations can be facilitated by • offloading the critical timing to an external device • doing worst case timing analysis • use longest and shortest paths together