TSF Upgrade Project Overview

An overview of the TSF Upgrade Project timeline, milestones, and current status, including history, UK manpower, test timetable, production schedule, and summary of achievements & concerns.

TSF Upgrade Project Overview

E N D

Presentation Transcript

TSF Upgrade Project Overview Resources Plans and Timetable Hardware + Tests : Scott Kolya VHDL + Tests: Marc Kelly Bristol – Manchester - RAL Nicolo de Groot 11th April 2003 Final Design Review

History • September 2001: First proposal to PPRP. Based on daugthercards. Estimated costs £200k. Decision postponed. • December 2001: Approval for prototype funding (£27k). Up to 60k for production. • 2002: Trigger Upgraded postponed by one year, use this to make a cheaper board, no daughtercards, only 5 FPGAs. • December 2002: New Proposal to PPRP

Funding • Full production costs, estimated at £75k are approved by the PPRP, after we have demonstrated a working prototype • An amount of £23k has been released to order components with a long lead time (FPGAs)

Current Status: Prototype • 3 Chips, complete functionality needed for testing • Boundary Scan OK • Currently under test at SLAC (see Scott’s and Marc’s presentation)

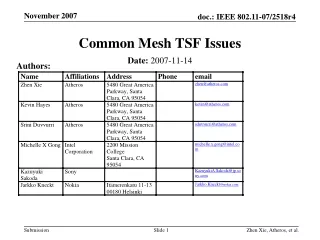

UK Manpower • Physicists / Management • Roger Barlow, Manchester • Nicolo de Groot, RAL • Technical effort • Jamie Boyd, Postdoc, Bristol, 100% • Dave Mercer, Engineer, Manchester, 50% • Scott Kolya, Postdoc, Manchester, 50% • Marc Kelly, Bristol, 100% • These are time integrated averages.

Test Timetable The schedule represents our most optimistic timetable. It is dictated by the need to have a full system test before the end of the run (July) using a pre-series. In order to be able to do so we will instrument 6 of our prototype boards for the system tests. The test schedule will look like this: • Last week April: completion engine firmware, completion test VHDL • First week May: system tests at SLAC • End of this week: start assembly of 6 test boards: 2 weeks • End of May: boards to SLAC for full system test • June: testing • This assumes the prototype boards will be usable for the full system test. (so far, so good)

Production Timetable • End June: final design, start production • End August: pre series ready • Early September: test at SLAC • September: production • October: delivery • Currently beam back on September 5th. Can we speed things up ?

Summary • Complete redesign of TDF completed. • Prototype is there, testing. • Confident that we can deliver. • Some worries about the schedule. • Maybe on time but under budget