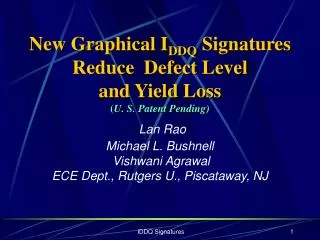

Enhancing Yield in VLSI Chips Through New Graphical IDDQ Signatures

E N D

Presentation Transcript

New Graphical IDDQ Signatures Reduce Defect Leveland Yield Loss(U. S. Patent Pending)Lan RaoMichael L. BushnellVishwani AgrawalECE Dept., Rutgers U., Piscataway, NJ IDDQ Signatures

IDDQ Testing VDD = 5V IDD IDDQ fault Ground Ref. Chakravarty and Thadikaran, 1997 IDDQ Signatures

IDDQ (microA) vs. Vector # A good chip A bad chip IDDQ Signatures

Two Proposed Approaches: • New way #1 • Use 135 IDDQ test vectors, instead of 10-20 vectors in real production line, collect all current measurements and plot current as function of test vector index. • Use classifier software running on Automatic Test Equipment to classify chip as good or bad. • Without using ‘stuck-at fault’ voltage test, but keeping the other voltage tests. • New way #2 • Only use graphical IDDQ testing method defined above. Potentially large cost saving for VLSI chip manufacturing test. IDDQ Signatures

Economics Analysis* *With help from Dr. Phil Nigh, IBM. IDDQ Signatures

New Classification Features The shape of the entire curve of current measurements – • # of bands that measurements cluster into. • Width and separation of bands. • Current glitch or smearing detection among all IDDQ measurements. IDDQ Signatures

IIDDQ Distribution Over Vectors is not Gaussian IDDQ Signatures

Classification of DUT • Good devices • Devices passing all tests and all test steps. • Devices that fail wafer probe test, but pass packaged test and burn-in, (poor wafer probe registration). • Bad devices • Devices that failed the tests other than the IDDQ test. • Devices with extremely high IDDQ current. • IDDQ only • Devices that failed on the IDDQ test with less than the absolute IDDQ threshold. IDDQ Signatures

Good vs. Faulty Chip(Single Band) Smeared (noisy) single band of a bad chip Single band of a good chip IDDQ Signatures

Good vs. Faulty Chip(Single Band with Spike) Good Chip Plot Faulty Chip with Noise Spikes IDDQ Signatures

Good vs. Faulty Chip (Multiple Bands) Good 2 Band Chip Faulty 2 Band Chip with Smearing IDDQ Signatures

Statistics (A) Method Test Escape(8) Overkill (8) Test escape (25) Overkill (25) Test escape (450) Overkill (450) Single-threshold 6.4% 1.6% 6.8% 2.2% 7.5% 2.3% Current difference 35.3% 3% 34% 3% 35% 3.1% IDDQ (4 A) 8.9% 1.1% 8.6 0.8% 8.6% 1.0% IDDQ (ó =0.35) 7.3% 6.6% 7% 6.7% 7.6% 6.8% Graphical IDDQ 5.0% -2.8% 5.4% -2.7% 5.97% -2.5% Comparing IDDQTest Methods Observation: The absolute threshold value is not critical for this technique. IDDQ Signatures

Test Method Efficiencies % Bad Chips Detected 8 mA450 mA 52.6 % 61.5% 71.3 % 83.4% 70.3 % 82.2% 93.6 % 93.5% 96.1 % 96.1% 75.8% 88.6% Statistics Test Method IBM Functional Test IBM Stuck-at Test IBM Delay Test IBM IDDQ Test Graphical IDDQ Test IBM (functional+ stuck-at+delay) IDDQ Signatures

Test Vector Set Truncation Results Proper selection of test vector set can further improve the test quality. IDDQ Signatures

Conclusion • Gaussian distribution of IDDQ measurements may not be true. • We present a new way of IDDQ testing with lower test escape and lower yield loss (overkill rate). • The new method • does not rely on a single threshold or a single delta threshold, but on the shape of the measurement set, hence it is promising for deep submicron technology; • can replace at least some voltage tests; • the accuracy can be further improved by careful choice of the test vector set. IDDQ Signatures

Thank you! IDDQ Signatures