Chap. 13 Multiprocessors

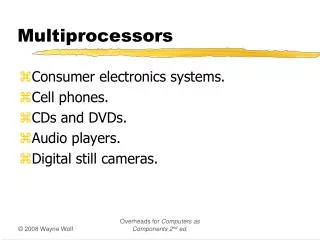

Chap. 13 Multiprocessors. 13-1 Characteristics of Multiprocessors Multiprocessors System = MIMD An interconnection of two or more CPUs with memory and I/O equipment a single CPU and one or more IOPs is usually not included in a multiprocessor system

Chap. 13 Multiprocessors

E N D

Presentation Transcript

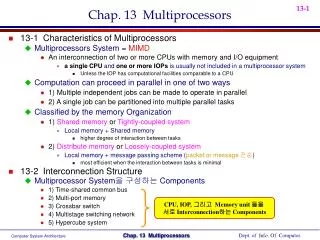

Chap. 13 Multiprocessors • 13-1 Characteristics of Multiprocessors • Multiprocessors System = MIMD • An interconnection of two or more CPUs with memory and I/O equipment • a single CPU and one or more IOPs is usually not included in a multiprocessor system • Unless the IOP has computational facilities comparable to a CPU • Computation can proceed in parallel in one of two ways • 1) Multiple independent jobs can be made to operate in parallel • 2) A single job can be partitioned into multiple parallel tasks • Classified by the memory Organization • 1) Shared memory or Tightly-coupled system • Local memory + Shared memory • higher degree of interaction between tasks • 2) Distribute memory or Loosely-coupled system • Local memory + message passing scheme (packet or message 전송) • most efficient when the interaction between tasks is minimal • 13-2 Interconnection Structure • Multiprocessor System을 구성하는 Components • 1) Time-shared common bus • 2) Multi-port memory • 3) Crossbar switch • 4) Multistage switching network • 5) Hypercube system CPU, IOP, 그리고 Memory unit 들을 서로 Interconnection하는 Components

Time-shared Common Bus • Time-shared single common bus system : Fig. 13-1 • Only one processor can communicate with the memory or another processor at any given time • when one processor is communicating with the memory, all other processors are either busy with internal operations or must be idle waiting for the bus • Dual common bus system : Fig. 13-2 • System bus + Local bus • Shared memory • the memory connected to the common system bus is shared by all processors • System bus controller • Link each local but to a common system bus Tightly coupled system

Multi-port memory : Fig. 13-3 • multiple paths between processors and memory • Advantage : high transfer rate can be achieved • Disadvantage : expensive memory control logic / large number of cables & connectors • Crossbar Switch : Fig. 13-4 • Memory Module의 I/O Port가 하나인 경우에 Crossbar Switch를 사용해야 함 • Block diagram of crossbar switch : Fig. 13-5 CPUs MM

Crossbar Switch 사용 예제 cluster cluster cluster cluster cluster cluster cluster Crossbar- Hierarchies cluster cluster cluster cluster cluster cluster cluster cluster cluster Cluster Node Node Node Node Node Node Crossbar PU CU 8 Network Interface I/O 4 8 Local Memory

Multistage Switching Network • Control the communication between a number of sources and destinations • Tightly coupled system : PUMM • Loosely coupled system : PUPU • Basic components of a multistage switching network : two-input, two-output interchange switch : Fig. 13-6 • 예제 )2 Processor (P1 and P2) are connected through switches to 8 memory modules (000 - 111) : Fig. 13-7 • Omega Network : Fig. 13-8 • 2 x 2 Interchange switch를 사용하여 N input x N output network topology 구성

Hypercube Interconnection : Fig. 13-9 • Loosely coupled system에서 사용 • Hypercube Architecture 예제 : Intel iPSC ( n = 7, 128 node ) • 13-3 Interprocessor Arbitration : Bus Control • Single Bus System : Address bus, Data bus, Control bus • Multiple Bus System : Memory bus, I/O bus, System bus • System bus : Bus that connects CPUs, IOPs, and Memory in multiprocessor system • Data transfer method over the system bus • Synchronous bus : achieved by driving both units from a common clock source • Asynchronous bus : accompanied by handshaking control signals

System Bus 예제 : IEEE Standard 796MultiBus • 86 signal lines : Tab. 13-1 • Bus Arbitration 신호선 : BREQ, BUSY, … • Bus Arbitration Algorithm : Static / Dynamic • Static : priority fixed • Serial arbitration : Fig. 13-10 • Parallel arbitration : Fig. 13-11 • Dynamic : priority flexible • Time slice (fixed length time) • Polling • LRU • FIFO • Rotating daisy-chain * Bus Busy Line사용 If this line is inactive, no other processor is using the bus

13-4 Interprocessor Communication & Synchronization • Interprocessor Communication • shared memory : tightly coupled system • Accessible to all processors : common memory • Act as a message center similar to a mailbox • no shared memory : loosely coupled system • message passing through I/O channel communication • Interprocessor Synchronization • Enforce the correct sequence of processes and ensure mutually exclusive access to shared writable data • Mutual Exclusion • Protect data from being changed simultaneous by two or more processor • Mutual Exclusion with Semaphore • Critical Session • Once begun, must complete execution before another processor accesses • Semaphore • Indicate whether or not a processor is executing a critical section • Hardware Lock • Processor generated signal to prevent other processors from using system bus

Semaphore를 이용한 shared memory 사용 방법 • 1) TSLSEM명령 실행 (Test and Set while Locked) • Hardware Lock 신호를 발생시키면서 SEM비트를 검사 • 2 memory cycle 필요 • : Test semaphore (semaphore를 레지스터 R로 읽어 들인다) • : Set semaphore (다른 processor의 shared memory 사용을 금지) • 2) R = 0인 경우 : shared memory is available R = 1인 경우 : processor can not access shared memory (semaphore originally set) • 13-5 Cache Coherence • Conditions for Incoherence : Fig. 13-12, 13 • Multiprocessor system with private caches • Write through : P2, P3 Incoherence • Write back : P2, P3, Main memory Incoherence P1이 X에 120 을 Write 하는 경우

Solution to the Cache Coherence Problem • Software 적인 방법 • 1) Shared writable data are non-cacheable • 2) Writable data exists in one cache : Centralized global table • Hardware 적인 방법 • 1) Monitor possible write operation : Snoopy cache controller • 참고 문헌 : • IEEE Computer, 1988, Feb. “Synchronization, coherence, and event ordering in multiprocessors” • IEEE Computer, 1990, June. “A survey of cache coherence schemes for multiprocessors”