MMX technology for Pentium

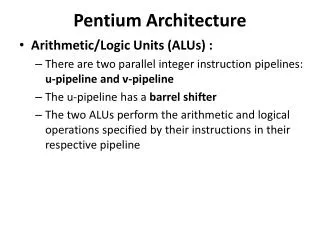

MMX technology for Pentium. Introduction. Multi Media Extension (MMX) for Pentium Processor Can be switched for multimedia computations working in Co processor mode with MMX instruction set The coprocessor works in SIMD instruction set processor for multi media applications

MMX technology for Pentium

E N D

Presentation Transcript

Introduction • Multi Media Extension (MMX) for Pentium Processor • Can be switched for multimedia computations working in Co processor mode with MMX instruction set • The coprocessor works in SIMD instruction set processor for multi media applications • Some MMX Applications are • motion video • combined graphics with video • Image processing • Audio and speech synthesis and compression • Video conferencing • Telephony • 2D and 3D graphics

MMX instruction set • SIMD instructions of type Arithmetic, comparison, conversion, logical, shift and data transfer • Instructions will start with letter P as first character • Instructions are appended with B, W or D • MMX instructions use dual operands and register set MM0 – MM7 • The result of operation is moved on to First operand

MMX arithmetic Instruction set • ADD • PADDB, PADDW, PADDD • PADDB MM1, MM2 adds the entire 64 bit contents of MM2 to MM1 byte by Byte and stores in MM1 • Any carries are dropped • Adding a byte A0H to 70H gives 110H , but the carry is dropped and byte will be 10H • Second operand can be a memory location containing 64 bit packed data

MMX arithmetic Instruction set (1) • SUB • PSUBB, PSUBW, PSUBD • PSUBB MM1, MM2 subtracts the entire 64 bit contents of MM2 to MM1 byte by Byte and stores in MM1 • Like PADD , PSUB also does not carry or borrow • Second operand can be a memory location containing 64 bit packed data • If the result of subtraction due to underflow and overflow errors result in 7FH (+128) for a overflow and 80H (-128) for underflow, Intel calls it as saturation

MMX arithmetic Instruction set (2) • MUL • PMULL, PMULH, • PMULLW MM1, MM2 multiplies the entire 16 bit LW contents of MM2 with LW of MM1 and stores the 32 bit result in MM1 • Like PADD , PSUB also does not carry or borrow • Second operand can be a memory location containing 64 bit packed data • PMADDWD instruction multiplies and adds. After multiplying four 32 bit results are added to get two 32 bit double word result.

MMX comparison Instructions • Two comparison instruction • PCMPEQ ( equal ) • PCMPGT ( greater than ) • Append it with B,W or D depending on the word length • Operands can be MMX register or memory location • These instruction does not change the flags; instead it changes the result operand filled with 000… or 111…

MMX conversion Instructions • Two basic conversion instructions • PACK >> convert data in Dword/ Qword in MMX packed format Available as • PACKSS ( signed saturation ) • PACKUS ( unsigned saturation ) • Can be appended with B, W, D • PUNPCK >> convert packed data to normal data word / byte available as • PUNPCKH ( unpack High data ) • PUNPCKL ( unpack Low data ) • To be used in combinations of WB ( word to byte ) or DW ( double word to word )

MMX Logic Instructions • PAND ( AND ) • PANDN ( NAND ) • POR ( OR ) • PXOR ( XOR ) • NO size extensions , BIT wise operation on all 64 bit data • Very powerful for bit manupulations

MMX shift Instructions • Logical shift and Arithmetic shift • Logic shifts are • PSLL ( Left Logic ) • PSRL (Right Logic ) • Variations are W, D and Q • Arithmetic shifts preserves the sign bit • PSLA ( left Arithmetic ) • PSRA ( right arithmetic ) • Example : PSLLD MM3,2 shifts the two 32 bit double word in MM3 left two places

MMX data transfer Instructions • Two data transfer instructions MOVED and MOVEQ • Transfers data between registers and memory • Example : MOVED ECX, MM2 moves the right most 32 bits of MM2 to ECX register • Example : MOVEQ MM2, MM3 moves the 64 bit of MM3 to MM2

MMX EMMS Instruction • EMMS ( empty MMX state ) • Sets 11 for tags >>> indicate that FPU barrel registers are empty • Must be executed before the return instruction so that FPU smoothly takes over • If not done FPU interrupt occurs and system crashes