Exceptions and Interrupts

Discover how interrupts and exceptions function in embedded systems, focusing on their definitions, types, and applications. Learn the difference between polling and interrupt-driven methods, how to manage I/O operations, and the significance of scheduling priorities based on importance. Understand servicing interrupts, the design of interrupt service routines (ISRs), and how to configure the interrupt vector table effectively. This overview is essential for anyone involved in programming embedded systems, especially with focus on the PSoC microcontroller architecture.

Exceptions and Interrupts

E N D

Presentation Transcript

Exceptional Circumstances • At home - how do you know when someone wants to talk to you on the telephone? • A. Periodically pick up the phone and see if someone’s there • This is known as polling • B. Wait for the phone to ring and then answer it • This is exception- or interrupt-driven

When Interrupting is Nice • Coordinating I/O operations • Notifies the CPU that an input is ready or an output can be changed • Timing • Periodic (clock-driven) interrupts remind the CPU of the passage of time • Multi-tasking • Updating counters • Timing during interactive programs • Errors • Interrupts can notify of error situations

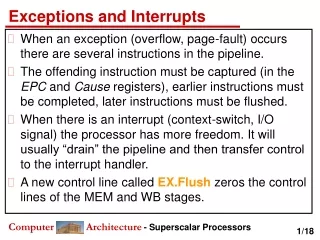

Exception Types • Hardware (called InterruptsorResets) • Reset • User-defined interrupt • Timer operations • CPU operations monitor failure • Software (not on PSoC) • Illegal instruction • Divide by zero • Overflow

I’m Not listening... • Interrupts can sometimes be ignored (or masked) • Good for when the CPU is doing something more important • When the interruptmask is set, interrupts are hidden (masked) and ignored • Interrupts may be prioritized • The fire alarm is more important than the oven timer which is more important than the telephone… • Non-maskable interrupts cannot be ignored • NMI’s take precedence and interrupt any task

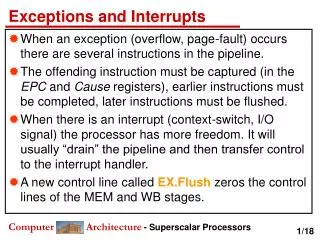

Servicing Interrupts and Exceptions • When an exception occurs • CPU decides whether to do anything • CPU saves current state • PC, Flag Register • Global interrupts disabled • Jump to interrupt service routine (ISR) • Execute routine • RETI - return from interrupt Works like a Call, except Flag register is saved, too. • Restore state • Flag Register (re-enables global interrupts) • Return to user program (restore PC)

Interrupt Vector Table • When an interrupt occurs, control of the program moves to the interrupt service routine (ISR) • Similar to a subroutine • But how do we know where the ISR is? • The address of the ISR is provided by the interrupt vector table • IVT has one entry for each type of interrupt • Each entry is indexed by interrupt type • PSoC vector table has four bytes for each entry • Usually holds a single “LJMP” instruction that passes control to the ISR

Address (16-bit) Vector # 1 Reset 0000h Low supply voltage 2 0004h Analog column 0 3 0008h Analog column 1 4 000Ch 5 Analog column 2 0010h 6 Analog column 3 0014h 7 VC3 0018h 8 GPIO 001Ch Interrupt Vector Table 0004h: LJMP to code for handling low voltage indicator 0010h: LJMP to code for handling analog col 2 interrupt 001Ch: LJMP to code for handling GPIO interrupt

Full PSoC Interrupt Vector Table Name: Identifies source of interrupt Device Availability Priority: If interrupts happen at the same time, highest priority interrupt wins Address: Address of interrupt vectorNote: Only 4 bytes, usually just an LJMP

Programming With Interrupts • Write the interrupt service routine • What action is to be performed when a particular interrupt happens? • End with RETI • Link the interrupt vector to the ISR • At interrupt vector location, write “LJMP myISR” • Usually taken care of by PSoC Designer • Write the main routine • Enable the interrupt to be serviced • Int_MSKx registers control various interrupts • Write a ‘1’ into the appropriate bit to enable the interrupt • See next slide for details • Globally enable interrupts • Set ‘GIE’ bit in flag register; use“M8C_EnableGInt” • Wait. That is, do nothing…

Interrupt Mask Registers • The registers INT_MSKx turn individual interrupts on or off • Write a ‘1’ to the appropriate bit to turn interrupts on • The 29466 chip we’re using has 4 analog columns and 4 digital rows (highlighted) • See useful equates in M8C.inc under “System and Global Resource Registers”

Whenever GPIO pin goes high, update and display a count 1. Select interrupt on pin in Design view(Don’t forget pull-down mode!) Example - GPIOISR 2. Write the GPIOISR: //ISR for the GPIO interruptPSoC_GPIO_ISR: inc [count] // increment count mov A,0// position LCD at 0,14 mov X,14 call LCD_1_Position mov A, [count] call LCD_1_PrHexByte // print out count reti // all done - return Interrupts can’t have parameters Must use globals 3. Link ISR to GPIO vector at 001C (Usually done already in boot.asm) org 001Ch ljmp PSoC_GPIO_ISR export count: export _main: area bss count: blk 1 // define counter area text _main: M8C_EnableGint call LCD_1_Start call LCD_1_Initor REG[INT_MSK0],%00100000 //’1’ in GPIO position loop: jmp loop 4. Write the initialization and main routine Do-nothing program!