Static Logic vs. Pseudo-nMOS

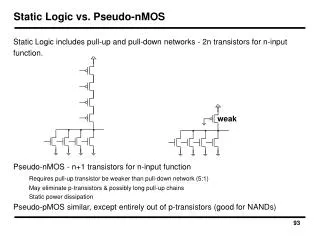

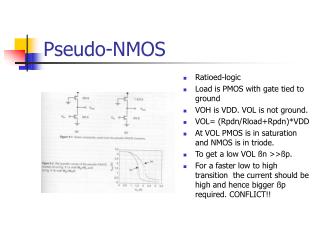

Static Logic vs. Pseudo-nMOS. Static Logic includes pull-up and pull-down networks - 2n transistors for n-input function. Pseudo-nMOS - n+1 transistors for n-input function Requires pull-up transistor be weaker than pull-down network (5:1)

Static Logic vs. Pseudo-nMOS

E N D

Presentation Transcript

Static Logic vs. Pseudo-nMOS Static Logic includes pull-up and pull-down networks - 2n transistors for n-input function. Pseudo-nMOS - n+1 transistors for n-input function Requires pull-up transistor be weaker than pull-down network (5:1) May eliminate p-transistors & possibly long pull-up chains Static power dissipation Pseudo-pMOS similar, except entirely out of p-transistors (good for NANDs) weak 93

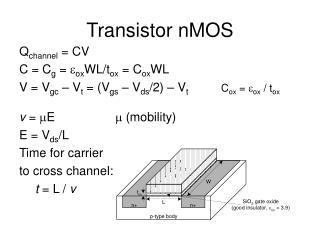

Building weak transistors Weakening transistors requires reducing width, increasing length (R=L/W) Create transistor with at least 5x greater resistance than others it fights against R=10/3 R=2/3 R=2/15 A Vdd R=10/3, less load on signal A 94

precharge precharge Dynamic Logic Like pseudo-nMOS except don't always pull up Initially charge output capacitance Need to make sure pull-down isn't fighting it Selectively discharge through pull-down network Avoids static power dissipation (and is faster), but more dynamic power 95

precharge precharge Charge Sharing Precharge A Redistribution of charge can degrade or change values Solution is to also precharge internal nodes Note: Moves late-arriving signals closer to output 96

weak precharge precharge Charge Leakage Compensate for leaking charge on output Advantages of dynamic logic (less transistors) but has static power dissipation Can avoid static power dissipation with inverter weak 97

precharge precharge precharge pull-down network pull-down network pull-down network Domino Logic Blocks in pseudo-nMOS style with inverter on output (non-inverting logic) Precharging all blocks - outputs equal to 0 Ensures no other pull-down networks are interfering with precharging When precharging is completed dominoes begin falling from first stage to last Final result is some output stay low while others go high 98

precharge pull-up network precharge pull-down network pull-down network precharge Zipper Logic Alternating blocks of n-type and p-type networks (provides an inversion) By alternating stages, during precharge each gate's network is turned off by precharge of previous stage Similar to domino but transistors are easier to pack since there are equal numbers of each type on average 99

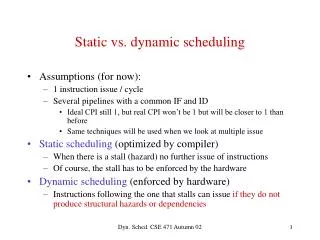

Static vs. Dynamic Logic Static + no charge sharing problems + no charge leakage problems + no static power dissipation - 2n transistors - series transistors always exist (slower) Dynamic + n+1 transistors - charge sharing - charge leakage - can have static power dissipation + potentially faster (eliminate series transistors) - more complex control (generate precharge signal) 100