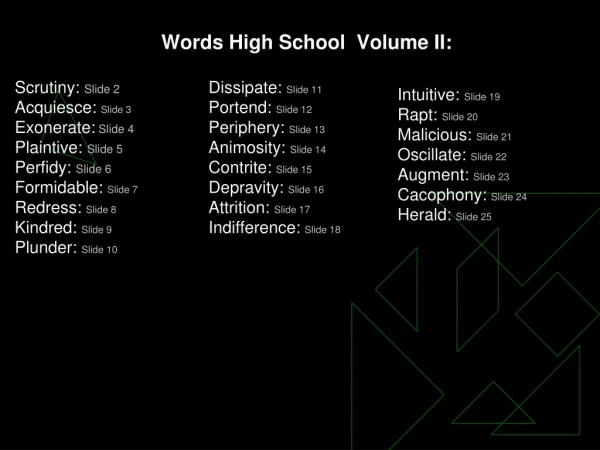

High-Volume FPGAs

High-Volume FPGAs. Xilinx Academy February 1999. Contents (7:45-9:45). High-Volume FPGA Organization Spartan Marketing Message Spartan Architecture SpartanXL Features Spartan Software Other Families AppLINX and Data Book Status. XC4000E 1996. High Volume Product Families. Spartan

High-Volume FPGAs

E N D

Presentation Transcript

High-Volume FPGAs Xilinx Academy February 1999

Contents (7:45-9:45) • High-Volume FPGA Organization • Spartan Marketing Message • Spartan Architecture • SpartanXL Features • Spartan Software • Other Families • AppLINX and Data Book Status

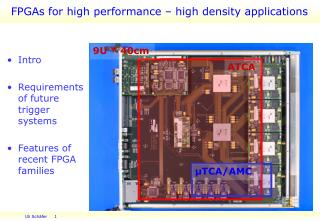

XC4000E 1996 High Volume Product Families Spartan 1Q 1998 SpartanXL 4Q 1998 New: in ‘98 No Compromises! Performance, RAM, Cores, Low Prices XC5200 1997 XC5200 1996 XC4000E 1997 Cost Effective Performance

High Volume FPGA Group Product Families: Spartan/XL: ASIC Replacement with RAM Plus … XC2000, XC3000, XC5200 Key Contacts: Primary Secondary Spartan/XL Jay Aggarwal Steve Sharp Kurt Wong XC2000/3000/A/L: Ed Chew Daniel Chan XC5200: Kurt Wong Steve Sharp Competitive Analysis: Mark Moran Ashok Chotai Application Support: Rick Mitchell Marc Baker Kim Goldblatt Tactical Marketing Frank Carbone Daniel Chan Denise Gibbons

No Compromises • High Performance • Up to 80 MHz system performance • On-Chip SelectRAMTM • Wide range of IP and CORE solutions • PCI LogiCORE + AllianceCORE • Fully integrated software support • Alliance and Foundation Series software • Volume Pricing competitive with ASICs Addresses the key needs of high volume logic users

Spartan Series Breaks The Mold to Penetrate New Applications • Simultaneous world-wide rollout (Jan 12, 98) • Extensive use of alternative media to reach broad audience • Sales kits, billboards, airport kiosks, ads, disti promos, web pages

Xilinx Spartan Series FPGAs Advanced Process Technology Xilinx 4000 Heritage 80 MHz Performance On-chip SelectRAM Software and cores Smallest die size Low packaging cost Low test cost Total Cost Management

Total Cost Management • Leading edge process technology • Smallest die size of any FPGA with on-chip RAM • Focused package offering • Low-power architecture allows use of highest volume plastic packages • PLCC, VQ, TQ, PQ, BGA • Streamlined test flow • Lower cost test hardware • Built-in self test features • Shorter test times • Optimized manufacturing flows

Spartan Series Opens New Markets and Applications • No compromises: • Performance • On-chip RAM (SelectRAM) • CORE support • Low cost • Xilinx’s 2nd-generation ASIC alternative • Drive volumes higher • Aggressive pricing • Price leader for mainstream low-density FPGA market

FPGA Design Win FocusSelect Family Based on Logic Cells Spartan/XL XC4000XLA/XV Virtex V50 V100 V150 V200 V300 V400 V600 V800 … V1000 40110XV ... 40250XV 4013XLA 4020XLA… 4085XLA S05/XL S10/XL S20/XL S30/XL S40/XL 20,000 28,000 238 1500 Estimated design size (logic cells)

Existing Design Strategy XC4000E Do Nothing Different Do Nothing Different Do Nothing Different XC4000XL XC5200 Do not convert existing designs to Spartan

All Spartan Family devices available Faster SpartanXL -5 coming soon -4 devices available now Enables 33 MHz PCI LogiCORE COREs and software available All Spartan Family devices in Base packages Spartan Series Is Here Today

Spartan Series Roadmap Without Compromises • Pricing competitive with ASICs • High Performance • On-chip SelectRAMTM • PCI LogiCORE + AllianceCORE Higher Speed Lower Power Power Down Mode Spartan $395 per 5K gates SpartanXL $295 per 5K gates 0.5 3LM Higher Density + More Features 5 Volt Price SpartanII up to 100K gates Spartan Next Generation up to 200K gates 0.35 5LM 3.3 Volt 0.25 5LM 0.18 2.5 Volt 1.8 Volt 1998 1999 2000 *Prices are for 100K units, slowest speed, lowest cost package

1997 1998 1999 2000 2001 2002 Priced for High-Volume Leadership 200K • New Applications • Set Top Box • DVD • Digital Camera • PC Peripherals • Consumer Electronics 100K Density (System Gates) 60K 100K 60K 25K 40K 10K Gates/$ in 2002! 15K 100K unit volume price projections

Identifying the Spartan Arena • What are typical ASIC densities? • What are typical ASIC clock speeds? • What packages are most common for ASICs? • What cores are popular for ASICs and how often are they used?

Spartan Arena Covers ASIC Designs Up To 40,000 Gates The Spartan Arena Dataquest 1997 Gate Array Design Starts by Gate Count

Spartan Arena Covers ASIC Designs Up To 80 MHz The Spartan Arena Dataquest 1997 ASIC Design Starts by Average Clock Speed

Spartan Arena Covers ASIC Designs from 84-256 Pins The Spartan Arena Dataquest 1997 ASIC Design Starts by Pin Count

Spartan Arena Addresses Most Popular ASIC Cores Many CORES require RAM (PCI, DSP, USB, etc.) The Spartan Arena Dataquest 1997 ASIC Designs By Core Usage

Identifying the Spartan Arena of ASIC Designs • Up to 40,000 system gates • Up to 80 MHz system performance • 84-256 package pins • RAM and/or COREs used • Up to 200K units/year

The Battlefield: Gates vs. I/Os ASIC WINS SPARTAN WINS! “The Spartan Arena”

Leverage Your Strengths:On-chip RAM Expands the Spartan Arena On-chip RAM “The Spartan Arena”

Spartan Series Changes the Battlefield for ASIC Designs • Leverage Spartan Series FPGA price leadership • Focus on high-I/O applications • Leverage on-chip RAM and COREs • Leverage FPGA benefits against ASICs • In-system programming, field upgrades, easy prototyping • No ASIC can deliver these benefits!

Spartan Series Makes Altera Play By Our Rules Xilinx Altera Altera still using “2 family” compromise strategy Design Requirement? Design Requirement? Gates-only On-Chip RAM Performance On-Chip RAM Performance Low Cost FLEX 6K FLEX 10K Low cost High cost

Spartan Series Features Eliminate Competitive FPGAs • Goal: Leverage on-chip RAM and COREs against other FPGAs • Tactic: Establish on-chip RAM as an absolute requirement for ASIC-alternative FPGA solutions • Used in 75% of ASIC designs • Used in many FPGA COREs • Spartan Series delivers on-chip RAM at ASIC prices

Use Spartan Series Advantages In The Quoting Process • Use “bracketing” in quotes to show options • Quote a multiple device sizes (downward) • Quote prices based on timeframe for orders • Quote different voltage options (Spartan vs. SpartanXL) • Quote volume stepped pricing • Volume price steps strictly enforced Project Aggressive Future Pricing

Call To Action • Find ASIC applications in the Spartan Arena and design-in Spartan Series FPGAs • Win back FLEX 10K 5-volt sockets • Keep FLEX 6K from getting any high-volume design wins

Spartan FPGA Architecture • Array of Configurable Logic Blocks (CLBs) • Perimeter Input/Output Blocks (IOBs)

CLB • Two Look-Up Tables (LUTs) create any function of four inputs • Two dedicated flip-flops

IOB IK EC

Single-Port RAM • Registered write • Asynchronous read

Dual-Port RAM Added:

Interconnect • Channel interconnect of varying lengths • “Segmented” interconnect minimizes capacitance • Maximizes speed and minimizes power • Single/double- length lines and long lines

Configuration • Single “Mode” Pin on 5V Spartan • High (default) = Slave Serial • Externally-controlled configuration • Low = Master Serial • FPGA-controlled configuration (from SPROM) • M1 pin on 3V SpartanXL enables parallel Express Mode • Mode pin(s) cannot be used as I/O • JTAG configuration supported

Mode Pins XC4000 Spartan SpartanXL M0 Master Serial Master Serial /Slave Serial /Slave Serial M1 Don’t Connect /Express M2 Don’t Connect /Powerdown

Pinouts • PQ208 pinout has been optimized • New pinout adds up to 9 I/Os, 8 VCCs • Optimizes noise • Other packages are not pinout- compatible with XC4000E due to MODE pin

Xilinx Spartan Series 5 Volt -> XCS05 XCS10 XCS20 XCS30 XCS40 3.3 Volt -> XCS05XL XCS10XL XCS20XL XCS30XL XCS40XL System Gates 2K-5K 3K-10K 7K-20K 10K-30K 13K-40K Logic Cells 238 466 950 1368 1862 Max Logic Gates 3,000 5,000 10,000 13,000 20,000 Flip-Flops 360 616 1120 1536 2016 Max RAM bits3,200 6,272 12,800 18,432 25,088 Max Avail. I/O 77 112 160 192 205 Performance 80MHz 80MHz 80MHz 80MHz 80MHz No Compromises: Performance, RAM, Cores, and Low Price

Spartan Series Footprint Compatibility • Highest volume ASIC plastic packages • Footprint compatible in common packages 5 Volt XCS05 XCS10 XCS20 XCS30 XCS40 3.3 Volt XCS05XL XCS10XL XCS20XL XCS30XL XCS40XL 84 pinPC84 PC84 100 pin VQ100 VQ100 VQ100 VQ100 144 pin TQ144 TQ144 TQ144 208 pin PQ208 PQ208 PQ208 240 pin PQ240 PQ240 256 pin BG256 BG256 Underlined = available in Industrial range

Spartan Naming • Logic cells are the best comparison metric • Will be used in all collateral and comparisons • Spartan part name uses “System Gates” • Includes both RAM and Logic • Top end of current “gate range” • Matches ASIC industry terminology (+ HardWire) • Consistent with future FPGA families XCS##XL-3PC84C XL = 3.3 Volt no XL = 5 Volt XCS = Spartan ## = System Gates

Spartan Speed Grades • Spartan speed grades increment from an arbitrary number (“-3”, “-4”) • No correspondence to a physical delay • Current XC4000 “-1”/”-09” do not correspond to LUT delay • LUT alone does not reflect overall clock speed or routing speed

Spartan Speed Grades • Higher Spartan speed grade = higher performance SpartanXL-5 E-1 Spartan -4 SpartanXL-4 E-2 Spartan -3 Performance -3 -4 5200 4000E Spartan,5V SpartanXL,3V

Spartan -4 Benchmarks • Pin-to-Pin I/O speed is fast

Spartan Differences from XC4000E • No Asynchronous RAM • No RAM16X1, RAM32X1 • Only RAM16(32)X1S, RAM16X1D (synchronous) • No Edge Decoders (wide AND of I/Os) • No DECODEx • No Wired-AND of BUFTs • No WANDx or WOR2AND • No Parallel Configuration Modes (only serial) • Mode Pins Not Usable as I/O • No MD0, MD1, MD2

Spartan Cannot Fit an Existing XC4000 Socket • Different pinout due to Mode pins • Different PQ208 pinout • Different package offering • Different functionality • Different bitstreams • Different timing

Global Clock Buffers Device BUFGP BUFGS BUFGLS BUFGE Spartan 4 4 0 0 SpartanXL 0 0 8 0 XC4000X 0 0 8 8 • General recommendation: Design with BUFG • Software chooses appropriate specific buffer • BUFGP/BUFGS will convert to BUFGLS automatically for SpartanXL target

SpartanXL CLB Latch • CLB flip-flops can be used as latches • LD, etc. components in SpartanXL library • Simplifies use of HDL synthesis • Similar to XC4000X

SpartanXL Interconnect • Carry only propagates upward • Significantly higher speed • Similar to XC4000X • Standard long line can be used to continue at the bottom of the next column • Datasheet figure shows upward carry only • Text describes that it is bidirectional in the 5V Spartan family • All other device routing is identical to 5V Spartan family