A BIST Scheme for FPGA Interconnect Delay Faults

150 likes | 329 Vues

A BIST Scheme for FPGA Interconnect Delay Faults. Chun-Chieh Wang, Jing-Jia Liou, Yen-Lin Peng , Chih-Tsun Huang, and Cheng-Wen Wu. Laboratory for Reliable Computing (LaRC) Department of Electrical Engineering National Tsing Hua University Hsinchu, Taiwan 30013. Outline. Introduction

A BIST Scheme for FPGA Interconnect Delay Faults

E N D

Presentation Transcript

A BIST Scheme for FPGA Interconnect Delay Faults Chun-Chieh Wang, Jing-Jia Liou, Yen-Lin Peng, Chih-Tsun Huang, and Cheng-Wen Wu Laboratory for Reliable Computing (LaRC) Department of Electrical EngineeringNational Tsing Hua University Hsinchu, Taiwan 30013

Outline • Introduction • Objective • Proposed BIST architectures • Experimental results • Conclusions

Introduction • The causes of FPGA delay fault • More circuits operating at high speed • DSM processes have resulted in more defects affecting the delay • FPGA delay testing problem • Path delay fault model is not appropriate • Segment delay fault model is used • At-speed testing is practically difficult • Need BIST approach

Objective • Why test the interconnects of FPGA? • Delay faults are mostly associated with interconnects • Universal testing method • Application-independent testing methodology • The objective: • A BIST scheme for interconnect delay faults with minimal clock skew effects

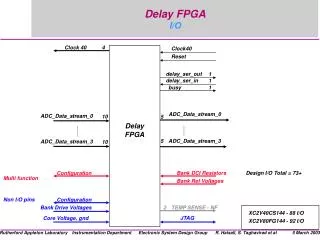

Proposed BIST Design (BIST1) • Assumptions: • The PUT has to be the longest path among all paths in the BIST • Ignore skew between FFs in a CLB

BIST BIST BIST ORA ORA ORA ORA ORA ORA BIST BIST BIST BIST BIST BIST ORA ORA ORA First phase Second phase Test Result Observation • Readback mechanism • The two phase approach

WE and NS Switch Testing Issues • The loop-back PUTs targeting WE and NS are too long • Shorter PUTs are connected between different CLBs • Need to validate clock skews

Clock Skew Validation • Using tested paths to validate clock • Change test clock: T’CLK = TCLK + TSkew • Violations can be detected when they cause strobe time to be earlier than TPath • Shortest path has small TSlack to detect small violations

Modified BIST Design (BIST2) • Assumptions: • The clock skews have been validated • The PUT is longest • Other paths have been tested

BIST type Target segments # of TCs Total All wire segments 1 16 BIST1 NE, WS, WN, and ES switches 40 1 All WE, NS switches 24 All wire segments 1 16 NE, WS, WN, and ES switches BIST2 36 2 Clock skew between 2 adjacent CLBs 4 2 All WE & NS switches 16 Experimental Results • Target device: a 14x14 Xilinx Spartan Series FPGA • Only single-length lines are considered • After TC reduction • BIST1 has lower utilization than BIST2

Segment Coverage • A metric to measure how much resources are covered by test configurations • BIST-based methods never cover segments involved with IOB

Statistical Delay Defect Coverage • Use Poisson distribution to model the fault distribution • Adopt a Monte Carlo process to produce samples • Effective statistical delay defect coverage (ESDDC) = Sdetected / Sfailed • Sdetected: total failed samples that have been detected • Sfailed: total failed samples

ESDDC Sample count: 10K Defect count (mean): 1.3 Slack: 10% of segment spec. FPGA size: 14 x 14

Conclusions and Future Work • We have proposed new BIST designs for FPGA interconnect delay faults • At-speed testing • Without being affected by clock skew • Easy implementation on different FPGA architectures • Test configurations are generated automatically • Future work: interconnect delay fault diagnosis