Logic and Digital Circuits: from Practice to Theory

530 likes | 646 Vues

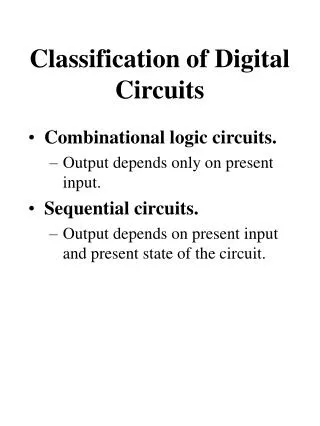

This comprehensive work by Gérard Berry delves into the intricate relationship between logic and digital circuits, tracing their evolution from practical applications to foundational theories. Covering topics such as combinational circuits, digital components, and system-on-chip architecture, this text serves as a valuable resource for professionals in electronics and computer engineering. By examining critical concepts like propagation delays and stabilization in acyclic networks, it bridges theoretical frameworks with practical implementations, offering insights into contemporary digital design challenges.

Logic and Digital Circuits: from Practice to Theory

E N D

Presentation Transcript

Logic and Digital Circuits: from Practice to Theory Gérard Berry http://www-sop.inria.fr/members/Gerard.Berry/ INRIA Sophia-Antipolis Collège de France, 2007-2008 and 2009-2010 Logic to the Rescue, Nancy, July 22nd, 2011

Digital Circuits PC microprocessors telephones, DVD, TV, GPS,... SoC = Systems on Chip Sorrce Intel G. Berry, Nancy

Combinational Gates and Circuits c a a b b and or xor mux not(a and b) (not a)and b mux(c,a,b) =(c and a) or ((not c) and b) s sa xor b xor c a b r c s(a and b) or(b and c) or(c and a) full adder G. Berry, Nancy

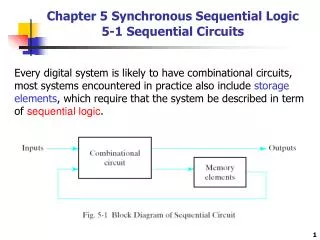

GO Combinational propagation 1 REQ OK 0 PASS TRY GO 1 GET_TOKEN PASS_TOKEN Since the network is acyclic, outputs stabilize in bounded time if inputs are kept constant Stabilization time is determined by the critical path G. Berry, Nancy

The Ripple-Carry Adder c= 0 s + 0 a 0 0 + b 0 c 1 Fornbits timen s + a 1 + 1 b 1 c 2 s + a 2 2 + b 2 c 3 G. Berry, Nancy

n n+1 0..n-1 s[0..n-1] a[0..n-1] n n+1 0..n-1 b[0..n-1] s’[0..n-1] n n n+1 n 0 1 s[n..2n] a[n..2n-1] n+1 n b[n..2n-1] 0 1 s’[n..2n] The von Neumann Logarithmic Adder G. Berry, Nancy

The von Neumann Logarithmic Adder For n bits time log(n) G. Berry, Nancy

The Register a a r ck ck reg(a) r a r a a0, a1, a2, ... r 0, a0, a1, a2, ... a r a a0, a1, a2, ... r 1, a0, a1, a2, ... G. Berry, Nancy

GO clock Sequential sampling 1 REQ OK 0 PASS TRY GO 1 GET_TOKEN PASS_TOKEN tick ! tick ! G. Berry, Nancy

GO clock Sequential sampling 1 0 REQ OK 0 0 PASS TRY GO 1 0 GET_TOKEN PASS_TOKEN tick ! tick ! G. Berry, Nancy

The Serial Adder 6 19 a ...00110 s ...10011 b ...01101 r 13 Serial Adder See the marvelous use of 2-adic numbers in “On Circuits and Numbers” by Jean Vuillemin G. Berry, Nancy

GO Boolean Equation View 1 REQ OK 0 PASS TRY GO 1 GET_TOKEN PASS_TOKEN OKREQandGO PASSnotREQand GO GOTRYorGET_TOKEN PASS_TOKENreg(GET_TOKEN) Waiting for the critical time solving the equations G. Berry, Nancy

Architecture functionality OK? performance OK? marketing OK? know-how reviews Excel / C prototypes software modeling model-checking theorem proving breakdown OK? performance OK? Micro-Architecture functionality OK? speed / area OK? power OK? random-directed test formal verification RTL Logic Design equivalent to source? circuits formal verification ATPG SAT test coverage ~100% ? DFT (test) connections? electrically OK? timing OK? Place&Route Design Rules Checking (DRC) $ 1,000,000 Masks packaging, testing Chips really works? ESTEREL G. Berry, Nancy

GO Combinational Circuit Proof Network 1 REQ OK 0 PASS TRY GO 1 GET_TOKEN PASS_TOKEN Each operator is a proof component Circuit graph of all proofs of outputs from inputs G. Berry, Nancy

Constructive Boolean Propagation Logic • Input vector I inputs → {0,1} • Formulae: Ieb Ie0 Ie1 Ie0 Ie1 Ie’0 Ie’1 Ie1 Ie0 Ie’0 Ie’1 III(I) Ie and e’1 Ie or e’1 I not e 0 I not e 1 Ie and e’0 Ie or e’1 Ie or e’0 Ie and e’0 Ie or not e1 ssi I e0 or I e1 X eIeb IXb G. Berry, Nancy

The ABRO Synchronization Example Emit O as soon A and B have arrived Reset this behavior each R Memory Write R : request A : address B : data O : write R / R / A / B / R / A B /O R / B /O A /O G. Berry, Nancy

The ABRO Synchronization Example Emit O as soon A and B have arrived Reset this behavior each R R / R / A / B / R / A B /O R / B /O A /O G. Berry, Nancy

The ABRO Synchronization Example Emit O as soon A and B have arrived Reset this behavior each R R / R / A / B / R / A B /O R / B /O A /O G. Berry, Nancy

The ABRO Synchronization Example Emit O as soon A and B have arrived Reset this behavior each R R / R / A / B / R / A B /O R / B /O A /O G. Berry, Nancy

The ABRO Synchronization Example Emit O as soon A and B have arrived Reset this behavior each R Priority problems: what if A, B, R together? R / R / A / B / R / A B /O R / B /O A /O G. Berry, Nancy

Esterel Linear Specification loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; halt when R; end loop A / B / A B / B / A / G. Berry, Nancy

Esterel Linear Specification loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; emit O; halt when R; end loop A / B / A B /O B /O A /O G. Berry, Nancy

Esterel Linear Specification loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; emit O; halt when R end loop R / R / A / B / R / A B /O B /O A /O R / G. Berry, Nancy

Esterel Linear Specification loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; emit O; halt when R; end loop loop abort { await A|| await B }; emit O; halt when R end loop R / R / A / B / R / A B /O B /O A /O copies = residuals Esterel = sharing of residuals R / G. Berry, Nancy

Esterel SyncCharts Linear Specification loop abort { await A|| await B }; emit O; halt when R end loop R/ B/ A/ /O Hierarchical synchronous concurrent automata (Synchronous Statecharts) G. Berry, Nancy

Linear vs. Exponential exponential explosion! flat automaton Hierarchical automaton linear G. Berry, Nancy

E’k p p’ k0 E E’k p; q p’; q E E’0 F’l p p’ q q’ E E E’UF’l p; q q’ E Logical (SoS) Semantics G. Berry, Nancy

E’k F’l p p’ q q’ E E sE E1 awaits awaits E E’ U F’max(k,l) p’ | q’ p | q E Logical (SoS) Semantics sE E0 awaits 0 E G. Berry, Nancy

suppressed by optimization The ABRO Circuit (Proof Network) loop abort { await A || await B }; emit O; halt whenR end loop G. Berry, Nancy

Optimizing Register Allocation b b e0 e2 • 1-hot encoding • state numberexplostion a a b b • log(n) bits for n states • canblow up the logic e1 e3 e0 10 e1 11 e2 01 e3 00 e0 01 e1 10 e2 11 e3 11 good bad n! possibilities, no heuristics ! G. Berry, Nancy

I O combinationallogic registers R The key: balancing logic and registers Esterel / SyncCharts structural encoding G. Berry, Nancy

The Secret: Linear Specification! loop abort { await A || await B }; emit O ; halt when R end loop One register per explicit wait good logic / register balance The better the program is written, the more efficient the circuit is! G. Berry, Nancy

Replacing Register by Logic Question: can we replace a given register by logic? Registers r1, r2,..., rn, reachability predicate (r1, r2,..., rn) 1. Question for r1 – looks difficult: f. b1, b2,..., bn.(b1, b2,..., bn) b1f(b2,..., bn) 2. Logical rephrasing– algorithmically much easier: (0, b2,..., bn) (1, b2,..., bn) 0 3. Iteration + heuristics Very efficient BDD-algorithms (Madre-Coudert-Touati) Yields results always better than manual designs G. Berry, Nancy

Cyclic Circuit from Resource Sharing O = if C then F(G(I)) else G(F(I)) C 1 0 F C 1 0 O I 1 0 G C Cyclic combinational circuits can be exponentially smaller than acyclic circuits for the same function G. Berry, Nancy

Symmetric Round-Robin Protocol req ok A only one okin req order after the register set to1 B ok req G. Berry, Nancy

Symmetric Round-Robin Protocol req ok A The 1 register changes every cycle B ok req G. Berry, Nancy

Symmetric Round-Robin Protocol (4) req ok ok req req ok ok req G. Berry, Nancy

Symmetric Round-Robin Protocol req ok Beware of the combinational cycle ! ok req G. Berry, Nancy

Symmetric Round-Robin Protocol req ok 1 The cycle is sound if at least a register is 1, since it is cut at an or gate ok req G. Berry, Nancy

Symmetric Round-Robin Protocol req ok The cycle is unsound if all registers are 0 ok req G. Berry, Nancy

The Three Kinds of Cyclic Circuits • 1. Electrically and logically sound (possibly under • input conditions) • ex: combinational part of the cyclic round-robin • if at least one register output is 1 2. Electrically and logically unsound X X X notX • combinational part of the cyclic round-robin • if all register outputs are 0 G. Berry, Nancy

The Three Kinds of Cyclic Circuits ToBe • Logically computes 1 in classical logic, • but computes nothing in constructive logic 3. Strange circuits Hamlet : ToBe ToBe or not ToBe • Electrically stabilizes to 1 for some gate • and wire delays, but notfor all delays ! G. Berry, Nancy

Cyclic Circuits Analysis When does a circuit stabilize for all delays? Which logical view is correct? How to relate logic to electricity? Theorem:with the right electrical delay model, electrical stabilization for all delays logical constructivity definedness w.r.t. ternary simulation G. Berry, Nancy

Ternary simulation 1. Interpret equations over 0, 1, with 0 and 1 (Scott’s information ordering) 2. Monotonically extend basic Boolean functions 01 10 0 1 1 0 01 11 1 1 0 1 1 0 01 11 1 1 undefinable in C, Java, ML ! 3. Compute the least fixpoint of the equation system G. Berry, Nancy

Theorem:constructive propagation ternary simulation • Solves good cyclic examples • Correctly rejects Hamlet • no constructive propagation • least fixpoint is ToBe • Questions: • Do they characterize electrical behavior? • How to model continuous-time signals? • What is the electrical meaning of ? • uninitialized? unstable? metastable? • non-deterministic? etc. G. Berry, Nancy

Modeling Continuous Signals • Continous time in R+, discrete values in B {0,1} • Signal s: R+→B satisfying • right-continuity: s(t) b >0. s[t,t+]b • non-Zenoness: finite number of changes for any [t,t’] i DEL o DEL(i,o) (R+→B) (R+→B) non-deterministic relation G. Berry, Nancy

UI : Upbounded inertial delay model(Brzozowski-Seger 1995) i o Inertiality: o cannot change without being unstable if o changes from not b to b at time t, then there exists > 0 s.t. i[t, t] b Propagation: output cannot be unstable for time D without changing if i[t1,t2) b for t2> t1+, then t[t1,t2]s.t. o[t,t2] b G. Berry, Nancy

i o o 0 1 2 3 4 5 6 7 G. Berry, Nancy

Theorem (Shiple-Berry): if all wires and gates have UI-delays, then constructiveness is equivalent to UI-stabilization ... but UI is non-compositional: delay→delaydelay 1 2 i All wires UI-stabilize to 1, but constructive propagation and ternary simulation yield for them G. Berry, Nancy

UN : Upbounded delay model(Mendler 2008) i o Inertiality:outputs cannot change without unstable if o changes from not b to b at time t, then there exists > 0 s.t. i[t, t] b Propagation: output cannot be unstable for time D without changing if i[t1,t2) b for t2> t1+, then t[t1,t2]s.t. o[t,t2] b G. Berry, Nancy