Wire Arrangement and Layout for Pixel.nSQPE Board: Insights and Future Directions

This document outlines the current status and arrangements of wires on the Pixel.nSQPE board presented by David Nelson. It discusses the challenges in organizing wire bundles, selection of wire gauges, and the baseline specifications of 28CCAL for data and 36Cu for cmd & clk signals. Future migration to 34AWG for all signals is anticipated but requires further study. Additionally, it touches upon the layout of current opto-boards, the integration of LVDS chips, and the need for collaboration with opto-chassis teams for continued progress.

Wire Arrangement and Layout for Pixel.nSQPE Board: Insights and Future Directions

E N D

Presentation Transcript

Pixel nSQPE-board Presented by David Nelson djn@slac.stanford.edu

Status • Arrangement of wires on board • Determined during board layout. • Bundle organization/wire gauges • Base line is 28 CCAL for data & 36 Cu for Cmd&Clk • Hopefully can migrate to 34AWG for all signals • More studies needed on wire selection • PP1 penetration and connector to opto-boards • No progress – need help from opto-chassis folks

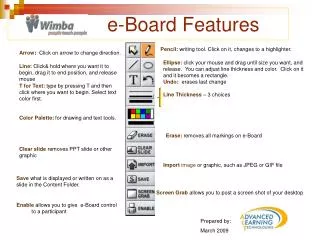

Layout of current opto-board Mounting holes 80 pin connector VDCs & DORICs

E-board • Wire bond LVDS chips • 8 chips on connector side Wire surface mount interface 8 LVDS buffers

LVDS Chip wire bond diagram • Received 12 LVDS die LVDS die