Deterministic Diagnostic Pattern Generation (DDPG) for Compound Defects

International Test Conference Santa Clara , CA, Oct 26-Oct 31, 2008. Deterministic Diagnostic Pattern Generation (DDPG) for Compound Defects.

Deterministic Diagnostic Pattern Generation (DDPG) for Compound Defects

E N D

Presentation Transcript

International Test ConferenceSanta Clara, CA, Oct 26-Oct 31, 2008 Deterministic Diagnostic Pattern Generation (DDPG) for Compound Defects Fei Wang1,2, Yu Hu1, Huawei Li1,Xiaowei Li1, Jing Ye1,21Key Laboratory of Computer System and ArchitectureInstitute of Computing Technology Chinese Academy of Sciences2Graduate University of Chinese Academy of Sciences Yu Huang33Mentor Graphics Corporation

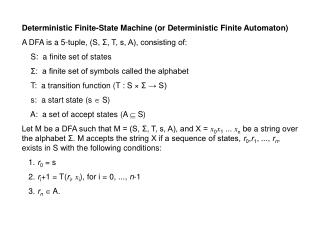

Purpose scan chain defects and system logic defects co-exist on the chip • Object • Faulty circuitcontains compound defects • Problem • How to diagnose scan chains when existing compound defects? • How to guarantee diagnostic accuracy, resolution and efficiency? • Method • Deterministically generate diagnostic patterns under certain constraints • Statistically failure analysis to locate the faulty scan cell

Outline • Background • Motivation • Related work • Our contributions • Proposed method • DDPG algorithm • Compound defect diagnosis process • Experimental results

Motivation • Why compound defect diagnosis • Both scan chains and system logic occupy significant area • Scan chains associated area: 30% [Kundu VTS’93] • Scan chain failures: 50% [Yang ICCD’05] • Assume system logic is fault-free will lead to misdiagnosis

Scan chain diagnosis Hardware based solutions Software based solutions Simulation based DDPG Partner scan chain Insert XOR gates Custom scan cell [Schafer VTS’92] [Edirisooriya VTS’95] [Narayanan ITC’97] Production test patterns Functional patterns Capture state Propagate state [Guo ITC’07] [Li TVLSI’05] [Huang ITC’07] [Tzeng TCAS’07] Related Work

Scan chain diagnosis Hardware based solutions Software based solutions Related Work Partner scan chain Insert XOR gates Custom scan cell Simulation based DDPG • High area and routing overhead • Unconventional DFT flow • Unguaranteed resolution • Unguaranteed accuracy • Impractical assumption: system logic is fault free!

Our Contributions • Features • First DDPG for compound defects • Effectively diagnose scan chains with dozens of system defects • Approach • Propagate the state of the targeted scan cell to multiple observation points • Statistical failure analysis to locate the faulty scan cell • Key results • Accurately diagnose faulty cell with dozens of system defects • Tolerate system logic faults without degradation of chain diagnostic resolution

Outline • Background • Motivation • Related work • Our contributions • Proposed method • DDPG algorithm • Compound defect diagnosis process • Experimental results

Fault Model Upstream Downstream SI SO 7 6 5 4 3 2 1 0

Basic Idea of DDPG SI SI Actual PI1=0 g x 1/0 0 G3 21 21 e x x 1/1 20 20 a x 0/0 x G1 19 19 x x x 18 18 STR Targeted cell b f 1/0 x x G2 16 16 Vulnerable-PPI 0/0 x x 15 15 c O3 O3 Protection-PPI 0/0 x x 14 14 x x x Trigger-PPI 13 13 x 1/0 Vulnerable-PPO 0 G4 8 8 PI2=1 x x 1/1 Protection-PPO 7 7 1/1 x x 5 5 i 1/0 1/0 1 G5 4 4 x x 1/1 3 3 x x x 0 0 SO SO System defect

Generate a pattern to propagate cellistate to n reliable observation points (ROP) within Output_Seti n=n-1 Y N n>1 ? Success? Y N Save the pattern, delete the n ROPs from Output_Seti N Output_Seti ∈ Ø? Y Delete the targeted cellifrom Suspect_Cell_Set N Suspect_Cell_Set∈ Ø? Y End DDPG Algorithm Overview Select cellifromSuspect_Cell_Set, build Output_Seti

DDPG Constraints-Loaded Value • Constraints on loaded values • Not constrain all scan cells on the faulty chain • only constrain the cells that sensitize fault propagation paths • The constrained scan cells can be anywhere on the faulty scan chain • Guarantee the patterns can be loaded correctly • The targeted scan cell can be sensitized and its statecan be propagated to ROPs

DDPG Constraints-Captured Value • Constraints on captured values • The state of ROPs can be safely unloaded • For stuck-atfaults, ROPs could be • downstream cells of LB in the faulty scan chain • good scan chains • POs • For timing faults, ROPs could be • all cells except the targeted cell in the faulty scan chain • good scan chains • POs 11110100

j j j SA0 SA0 SA0 Pick at least one observations points Pick 3 observation points Pick 2 from 3 DDPG Constraints-Sensitization • Sensitize Fault Propagation Path • off-path inputs of all the gates on propagation path are constrained to non-controlling values • Specify the minimum number of ROPs (n≥2)

Apply Constraints to Netlist SI SI PI1 h STR b f G4 8 G2 16 7 15 c 14 i G5 4 5 3 4 Sensitized path number ≥ 2 ? P1 P2 (b, f, h) j (b, f, i) P1P2 SA0 Constraint Circuit

patC16,1=3/10 patC16,2=4/10 patC16,3=3/10 LEP(C16,1)=1/3 LEP(C16,2)=4/4 LEP(C16,3)=2/3 Calculate the suspect score WLEP(C16)=7/10 patC16,1 patC16,3 C0 O3 C16 C21 C8 C4 patC16,2 Compound Defect Diagnosis Process Calculate a weight w(patCi,j) for each patternpatCi,j w(patCi,j)= # of ROPsCi,j / # of total ROPs Calculate a load error probability LEP(Ci,j) for each scan cell Ci LEP(Ci,j)=HCi,j / # of ROPsCi,j

Outline • Background • Motivation • Related work • Our contributions • Proposed method • DDPG algorithm • Compound defect diagnosis process • Experimental results

Experimental Setup • Five ISCAS’89 benchmark circuits • Key parameters • Each circuit hastwoscan chains • n=2, max(|Output_Seti|)=20 • Experimental steps For (cell=0;cell<L; cell++) { Inject a timing fault to cell Run DDPG and simulation, calculate Hit_Rate While (! misdiagnosis) { Randomly inject a SA1/SA0 fault to system logic Run DDPG and simulation, calculate Hit_Rate } }

Experimental Results Table 1. Hit_Rate of the proposed DDPG method A: system logic is fault-free B: one SA fault in system logic

Robustness Evaluation: s38584 (a) No system logic faults (b) 20 system logic faults (c) 40 system logic faults (d) 68 system logic faults

Robustness Evaluation: All CUTs Table 2. The number of faults injected into CUT when misdiagnosis happens

Diagnostic Resolutions Table 3. Diagnostic resolution (Average/Worst)

DDPG Time Table 4. Average pattern generation time (second) for a scan cell

Conclusions • First DDPG for compound defects • Statistical failure analysis for compound defects • Tolerate dozens of faults in system logic without degradation of chain diagnostic resolution