Strategies for Managing Diverse Hardware and Software Platforms in Computational Environments

This document explores best practices for dealing with various hardware and software platforms, focusing on abstraction layers, performance expectations, and the necessary details to expose to programmers and modelers. Key properties of hardware platforms, such as core types, memory architecture, and caching strategies, are highlighted. Furthermore, it discusses software characteristics, locking strategies, and the implications of abstraction layers like the JVM on performance predictability. Emphasis is placed on monitoring runtime adaptation and the potential benefits of collaboration between layers for improved efficiency.

Strategies for Managing Diverse Hardware and Software Platforms in Computational Environments

E N D

Presentation Transcript

Platform Abstraction Group 3

Question • How to deal with different types hardware and software platforms? • What detail to expose to the programmer? • What detail to expose to the modeler? • What are the layers in the abstraction?

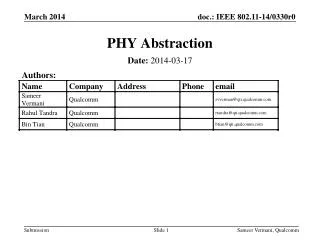

Properties of hardware platform 1. Number of cores 2. Type of cores (special purpose, GPU, CPU) 3. Memory bus (one, two, cross bars) 3! Cache lay-out (size, strategy, layers, …) 4. Memory architecture (NUMA, …) 5. Instruction set • (number indicates relevance to model) • Like to have: order relates to impact on accuracy • Priority list reflects how well it is understood

Properties of HW/SW(?) platform • Software locks in threads/processes • Locking strategy and lock density • Hardware execution or software implementation • Is there an abstraction layer such as a JVM? • Synchronization strategy / atomic operations used by Java, .Net, C++ vs. C libraries

Layers • Domain specific • Sometimes hardware features (e.g., branch prediction) are turned off to make performance predictable • All layers would profit from more collaboration. • E.g. Hyper-threaded cores (more on next slide) • Trade-off: complexity • Do we need standardization?

8 HT cores on Intel 4-core • We assume we are programming an application • We assume parallel tasks scale with the number of processing resources • Same task on 8 cores, hurts? • What expectation of performance should we have? • No direct relation between core count and performance • Should the programmer know about the HW platform?

Ctd. • We do not know how many ‘real’ cores we have? What is the core’s speed? … • Parallel behavior dependent on input • Monitoring and adaptation at runtime is necessary • There is a strong link between runtime adaptation and platform abstraction

Open problems • Can collaboration between layers improve the situation? • What gain is possible by collaboration? • What are the properties of the layers? • How can we then abstract these properties? • Who builds the ‘low’ level models? • Can the lower level provide a contract to satisfy our need for performance information?