Virtual Memory

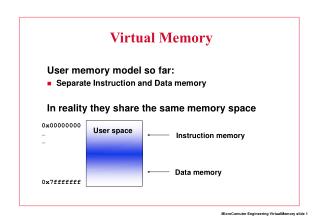

Virtual Memory. User memory model so far: Separate Instruction and Data memory In reality they share the same memory space. 0x00000000 … …. User space. Instruction memory. Data memory. 0x7fffffff. Virtual to Physical Address Mapping. 0x00000000 … 0x7fffffff. User space Instruction

Virtual Memory

E N D

Presentation Transcript

Virtual Memory User memory model so far: • Separate Instruction and Data memory In reality they share the same memory space 0x00000000 … … User space Instruction memory Data memory 0x7fffffff

Virtual to Physical Address Mapping 0x00000000 … 0x7fffffff User space Instruction and Data 2 GB Virtual address Physical address Physical memory Virtual memory 2 GB, HUGE amount Physical memory only 16 MB

Address Mapping CP0 MIPS PIPELINE Instr Data 32 32 Physical memory 16 Mb Arbiter 24-bit Physical Address 32-bit Virtual Address

Virtual Address User 1 2 GB Virtual Address 32-bit 31 10 9 0 Page 0 Page 1 Selects Page # x Offset within page #x …. Page x 1024 Bytes Page x Page n 22 10 2 Pages 2 Addresses

Virtual Memory Virtual Address Primary Memory 2 GB Physical memory 16 MB Page 0 Page 1 Page x …. Page 1 Page x Secondary Storage Hard Disk 2 GB Page n Page 0 Not Allocated Yet

Memory Resident Pages Only very few pages are RESIDENT in physical 31 10 9 0 Virtual 32-bit Address Selects Page # x Offset Address Translation of page #x 23 10 9 0 Physical 24-bit Address

Page Fault What about a NON RESIDENT page? • We know the Virtual Address, but: • No Physical Address, since the page is on Hard Disk (SWAPPED) What about a not allocated page • We know the Virtual Address, but: • We try to access a Virtual Address that we have not (yet) access to, that is an ERROR In both cases we get a PAGE FAULT

Page Table Virtual Address 2 GB Page Resident Physical Memory Page x Physical Addr [23:10] Page x Y …. Hard Disk Page y N Place on Hard Disk Page y For Non Resident Pages we get a PAGE FAULT

Swapping Virtual Address Physical Memory Resident 2 Gb …. Page y Secondary Storage Physical Addr [23:10] Page y Y Place on Hard Disk Page y The OS copies Page y to physical memory and restarts the failing user instruction

Page Fault and the OS A Page Fault is handled by the Kernel (OS) • 1) If physical memory not full • Copy the page from hard disk to a empty page X in physical memory • Update the Page Table, Resident = YES, Physical Addr [23:10]=X • Restart the failing instruction in the user program • 2) If physical memory full • Choose one page X from physical memory, store it on hard disk at XX • Update the Page Table (X), Resident = NO, place on HD = XX • Proceed with 1) What if page X is unchanged (only read operations), skip storing to hard disk, just set Resident = NO

Multiple User Processes Virtual memory n * 2 Gb Virtual address Physical address 16 Mbyte User 1 Page Table 1 0x00000000 … 0x7fffffff User n User 2 Page Table 2 0x00000000 … 0x7fffffff User 1 HD address …. User n Page Table n 0x00000000 … 0x7fffffff User n User 1 User 2 User 1 User 2

Where do we store the Page Tables? 16 Mbyte We store the Page Tables in Kernel memory • Protected from User access! User Memory Dirty Resident 22 Physical Addr [23:10] 2 entries huge array! Store only allocated pages D R Place on Hard Disk Kernel Memory Page Table 1 Page Table 2 Page Table n

Address Mapping CP0 User Memory MIPS PIPELINE Instr Data 32 32 24-bit Physical Address 32-bit Virtual Address User process 2 running Kernel Memory Page Table 1 Here we need page table 2 for address mapping Page Table 2 Page Table n

Translation Lookaside Buffer (TLB) CP0 On TLB hit, the 32-bit virtual address is translated into a 24-bit physical address by hardware We never call the Kernel! User Memory MIPS PIPELINE 32 32 24 D R Physical Addr [23:10] Virtual Address Kernel Memory Page Table 1 Page Table 2 Page Table n

Memory Hierarchy 14 Hardware is FAST but EXPENSIVE No need to use more than 2 entries STILL TO BIG! Make is smaller. Select a subset of the Page Table and store it in the TLB 16 Mb = 2 pages 14 User Memory Valid bit 24 V 22-bit Page # D Physical Addr [23:10] Kernel Memory Page Table 2

Address Translation • A TLB hit, we get a physical address • The Page # found in TLB and Valid entry (V-bit) • If a Write operation, set Dirty (D-bit) • A TLB miss, causes a TLB miss exception • If Page NOT Resident in Physical memory, • Page Fault and the OS slide • if page X is swapped to hard disk and X in TLB, clear V bit • If Page Resident in Physical memory • Find a free TLB entry and update it • 1) 22-bit Page #, set V-bit, clear D-bit, 14-bit physical address • If TLB full, chose a TLB entry • if D-bit, update Page Table Dirty bit, proceed with 1)

TLB control CP0 Control Signals TLB MISS R/W Page Table MIPS PIPELINE 32 Data bus Virtual Addr