REALITY

REALITY. Statistical Characterization of a High-K Metal Gate 32nm ARM926 Core Under Process Variability Impact. Memories and ssta. Local (Intra-die) Critical Path Delay Breakdown in ARM 926. 14% of clock period margin for intra-die variability:. 2.

REALITY

E N D

Presentation Transcript

REALITY Statistical Characterization of a High-K Metal Gate 32nm ARM926 Core Under Process Variability Impact

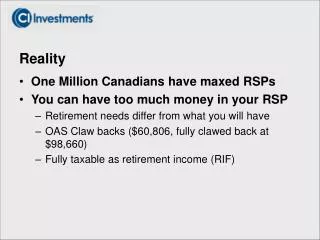

Memories and ssta Local (Intra-die) Critical Path Delay Breakdown in ARM 926 14% of clock period margin for intra-die variability: 2 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Memories and ssta Local (Intra-die) Critical Path Delay Breakdown in ARM 926 14% of clock period margin for intra-die variability: SRAM 2 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Memories and ssta Local (Intra-die) Critical Path Delay Breakdown in ARM 926 • SRAM variability dominates total intra-die variation by 75% • Yet, no approach can give a SSTA view on memories. • In this work, we quantify that memory contribution on an ARM926 core 14% of clock period margin for intra-die variability: SRAM 2 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Motivation / Objectives • Challenge: • Today’s deep submicron technologies suffer from variability • High-k / Metal Gate promising technology solution • Problem: • Assessment of process variability on product level difficult • Memories play important role • Commercial solutions to capture memory variability incomplete => Incomplete SSTA analysis Objectives: • Correctly characterize memory’s statistical contribution • Quantify variability’s impact of an ARM core timing including all 20+ memories 3 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Motivation / Objectives • Challenge: • Today’s deep submicron technologies suffer from variability • High-k / Metal Gate promising technology solution • Problem: • Assessment of process variability on product level is difficult • Memories play important role • Commercial solutions to capture memory variability are incomplete → Incomplete SSTA analysis Objectives: • Correctly characterize memory’s statistical contribution • Quantify variability’s impact of an ARM core timing including all 20+ memories 3 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Motivation / Objectives • Challenge: • Today’s deep submicron technologies suffer from variability • High-k / Metal Gate promising technology solution • Problem: • Assessment of process variability on product level is difficult • Memories play important role • Commercial solutions to capture memory variability are incomplete → Incomplete SSTA analysis Objectives: • Correctly characterize memory’s statistical contribution • Quantify variability’s impact of an ARM core timing including all 20+ memories 3 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Alternatives for dealing with memory blocks for statistical core characterization 4 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Alternatives for dealing with memory blocks for statistical core characterization .lib 4 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Alternatives for dealing with memory blocks for statistical core characterization Use of corners = No benefits of SSTA (as we will see) .lib 4 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Alternatives for dealing with memory blocks for statistical core characterization Use of corners = No benefits of SSTA (as we will see) Statistical simulation of entire SRAM impossible unless we have 100 days characterization time .lib 4 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Alternatives for dealing with memory blocks for statistical core characterization Use of corners = No benefits of SSTA (as we will see) Statistical simulation of entire SRAM impossible unless we have 100 days characterization time Considering single memory path as one big gate and run Statistical Spice .... Danger! = Parallel Paths! & Topology! .lib 4 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

device to core level fully statistical characterization flow Device variability Standard cell netlists Single Memory Path Netlist 5 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

device to core level fully statistical characterization flow Standard cell Liberty files Memory cell Liberty files Standard cell Liberty files Memory cell Liberty files Stat. Standard cell Libraries Statistical SRAM Libraries Statistical SRAM Modeling [DAC10] Calculate Memory-wide Statistics In-House Stat. Characterizer [PATMOS09, DAC11] Stat.Hspice, SiSmart/ELC/NCX,... Single Path Sensitivities (Stat. Hspice) Device variability Standard cell netlists Single Memory Path Netlist 5 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

device to core level fully statistical characterization flow New for Statistical Flows Standard cell Liberty files Memory cell Liberty files Standard cell Liberty files Memory cell Liberty files Stat. Standard cell Libraries Statistical SRAM Libraries Statistical SRAM Modeling [DAC10] Calculate Memory-wide Statistics In-House Stat. Characterizer [PATMOS09, DAC11] Stat.Hspice, SiSmart/ELC/NCX,... Single Path Sensitivities (Stat. Hspice) Device variability Standard cell netlists Single Memory Path Netlist 5 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

device to core level fully statistical characterization flow Statistical Timing / Power Report ARM gate level netlist DigiVAM (Design Compiler / ModelSim) In-House “SSTA” tool [ISQED09] Standard cell Liberty files Memory cell Liberty files Standard cell Liberty files Memory cell Liberty files Stat. Standard cell Libraries Statistical SRAM Libraries New for Statistical Flows Calculate Memory-wide Statistics Statistical SRAM Modeling [DAC10] In-House Stat. Characterizer [PATMOS09, DAC11] Stat.Hspice, SiSmart/ELC/NCX,... Single Path Sensitivities (Stat. Hspice) Device variability Standard cell netlists Single Memory Path Netlist 5 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Superposition of all conditions allows comparison of PVT: timing • Intra-die: distribution shifts in all corners: memory effects dominate (worst case cell statistics) • Inter-die: set final spread of distribution • Total: combination of the two (shift and spread) Critical Path Delay (memory& logic) 7 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Superposition of all conditions allows comparison of PVT: timing • Intra-die: distribution shifts in all corners: memory effects dominate (worst case cell statistics) • Inter-die: set final spread of distribution • Total: combination of the two (shift and spread) Critical Path Delay (memory& logic) 7 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Superposition of all conditions allows comparison of PVT: timing • Intra-die: distribution shifts in all corners: memory effects dominate (worst case cell statistics) • Inter-die: set final spread of distribution • Total: combination of the two (shift and spread) Critical Path Delay (memory& logic) 7 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Superposition of all conditions allows comparison of PVT: timing • Intra-die: distribution shifts in all corners: memory effects dominate (worst case cell statistics) • Inter-die: set final spread of distribution • Total: combination of the two (shift and spread) Critical Path Delay (memory& logic) 7 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Breaking out The Influence of Memories (Intra-Die) No variations (TT Corner for Logic and SRAM) Intra-die: Logic only (TT Corner for SRAM) 8 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Breaking out The Influence of Memories (Intra-Die) No variations (TT Corner for Logic and SRAM) Intra-die: Logic only (TT Corner for SRAM) Intra-die SRAM only (TT Corner for Logic) 8 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Breaking out The Influence of Memories (Intra-Die) No variations (TT Corner for Logic and SRAM) Intra-die: Logic only (TT Corner for SRAM) Intra-die SRAM only (TT Corner for Logic) SRAM and Logic Intra-die (both considered) 8 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Breaking out The Influence of Memories: Intra-Die variation No variations (TT Corner for Logic and SRAM) Intra-die: Logic only (TT Corner for SRAM) Intra-die SRAM only (TT Corner for Logic) Intra-die: SRAM & Logic 3s 0% 50% 75% 100% 8 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Breaking out The Influence of Memories: Intra-Die variation No variations (TT Corner for Logic and SRAM) Intra-die: Logic only (TT Corner for SRAM) Intra-die SRAM only (TT Corner for Logic) Intra-die: SRAM & Logic 3s 0% 50% 75% 100% SRAM 8 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM & Logic 3s 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM & Logic Inter-die :SRAM and Logic 3s 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM & Logic Inter-die :SRAM and Logic Total convolution intra- & inter-die (full core) 3s 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM & Logic Inter-die :SRAM and Logic Total convolution intra- & inter-die (full core) 3s 0% 40% 60% 100% 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM and Logic Inter-die :SRAM and Logic Total convolution intra- & inter-die (full core) 3s 0% 40% 60% 100% Intra-die 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Inter- and intra- die variation components in arm926 No variations (TT Corner for Logic and SRAM) Intra-die: SRAM and Logic Inter-die :SRAM and Logic Total convolution intra- & inter-die (full core) 3s 0% 40% 60% 100% Intra-die Intra-die SRAM 9 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

conclusions • Variability impact of 32nm HK-MG technology on a ARM926 quantified: • Intra-die: Total: • 75% 30% • Risk of under/over- design if margin concluded from SRAM typical/worst case corner only • State-of-art (in-house) statistical memory characterization used for SRAM .lib generation SRAM 10 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

conclusions • Variability impact of 32nm HK-MG technology on a ARM926 quantified: • Intra-die: Total: • 75% 30% • Risk of under/over- design if margin concluded from SRAM typical/worst case corner only • State-of-art (in-house) statistical memory characterization used for SRAM .lib generation SRAM Intra-die 10 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

conclusions • Variability impact of 32nm HK-MG technology on a ARM926 quantified: • Intra-die: Total: • 75% 30% • Risk of under/over- design if margin concluded from SRAM typical/worst case corner only • State-of-art (in-house) statistical memory characterization used for SRAM .lib generation SRAM Intra-die Intra-die SRAM 10 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

conclusions • Variability impact of 32nm HK-MG technology on a ARM926 quantified: • Intra-die: Total: • 75% 30% • Risk of under/over- design if margin concluded from SRAM typical/worst case corner only • State-of-art (in-house) statistical memory characterization used for SRAM .lib generation SRAM Intra-die Intra-die SRAM 10 Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011

Thank you! Statistical Characterization of a High-K Metal Gate 32nm ARM926 -- DAC User Track 2011