VHDL Descriptions: Serial Transmission and Sequence Detection

This lecture provides insights into VHDL descriptions, emphasizing Exercise 07.08, which focuses on designing a circuit for a serial transmission line. The design samples incoming bits at each clock cycle and asserts an output signal when the sequence '010' is detected. Students are encouraged to attempt the exercise independently, leading to a deeper understanding of VHDL principles. Further readings are suggested for those interested in a systematic approach to VHDL coding, enhancing their grasp of combinational and sequential block descriptions.

VHDL Descriptions: Serial Transmission and Sequence Detection

E N D

Presentation Transcript

Lecture 9.2 Paolo PRINETTO Politecnico di Torino (Italy)University of Illinois at Chicago, IL (USA) Paolo.Prinetto@polito.it Prinetto@uic.edu www.testgroup.polito.it Some examples

Goal • This lecture presents some example of VHDL descriptions. • In particular, a same exercise (namely Exercise 07.08) is described and synthesized at several abstraction levels and description domains.

Prerequisites • Lecture 9.1

Homework • Students are invited to try to solve the exercises by themselves, before looking at the proposed solutions • As a further set of exercises they are invited to describe, in VHDL, the RT level combinational and sequential blocks, presented in Lecture 5.1 and 5.3, respectively.

Further readings • Students interested in a systematic approach to VHDL coding are invited to refer to • M. Keating, P. Bricaud: “Reuse Methodology Manual for System-on-a-Chip Designs (2nd edition),”Kluwer Academic Publisher, Norwell, MA, USA, 2000, (chapter 5, pp. 73-125)

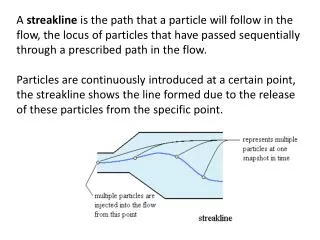

010 Exercise #07.08 • On a serial transmission line X, bits are transmitted synchronously w.r.t. a clock signal CLK, one bit per clock cycle. • A circuit to be connected to the serial line is to be designed. It samples the line X at each clock cycle. Whenever the sequence ‘010’ has been received, it asserts its output signal Z for one clock cycle. • A ‘0’ can be used, at a same time, as the last bit of a sequence and as the first bit of the next one.

Entity definition • library IEEE; • use IEEE.std_logic_1164.all; • entity seq_rec is • Port ( • clock, x, reset : in std_logic; • z : out std_logic • ); • end seq_rec;

Behavioral description system RT logic Behavioral description1 processregistered inputs behavior structure physical

Behavioral description1 processregistered inputs • architecture behav of seq_rec is • signal val : std_logic_vector (2 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset = '1' then • val <= (others =>'0'); • z <= '0';

Behavioral description1 processregistered inputs • architecture behav of seq_rec is • signal val : std_logic_vector (2 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset = '1' then • val <= (others =>'0'); • z <= '0';

Behavioral description1 processregistered inputs (cont’d) • elsif (clock'event and clock='1') then • val<= x & val (2 downto 1); • if (val = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end if; • end process; • end behav;

Behavioral description1 processregistered inputs (cont’d) • elsif (clock'event and clock='1') then • val<= x & val (2 downto 1); • if (val = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end if; • end process; • end behav;

Behavioral description1 processregistered inputs (cont’d) elsif (clock'event and clock='1') then val<= x & val (2 downto 1); if (val = SEQUENCE) then

Behavioral description system RT logic Behavioral description1 processnon-registered inputs behavior structure physical

Behavioral description1 processnon-registered inputs • architecture behav of seq_rec is • signal val : std_logic_vector (1 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset = '1' then • val <= (others =>'0'); • z <= '0';

Behavioral description1 processnon-registered inputs • architecture behav of seq_rec is • signal val : std_logic_vector (1 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset = '1' then • val <= (others =>'0'); • z <= '0';

Behavioral description1 process non- registered inputs (cont’d) • elsif (clock'event and clock='1') then • val<= x & val(1); • if ((x & val) = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end if; • end process; • end behav;

Behavioral description1 process non- registered inputs (cont’d) • elsif (clock'event and clock='1') then • val<= x & val(1); • if ((x & val) = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end if; • end process; • end behav;

Behavioral description1 process non- registered inputs (cont’d)

Behavioral description1 process non- registered inputs (cont’d)

Behavioral description1 process non- registered inputs (cont’d) elsif (clock'event and clock='1') then val<= x & val(1); if ((x & val) = SEQUENCE)

Behavioral description system RT logic Behavioral description2 process behavior structure physical

Behavioral description2 process • architecture behav of seq_rec is • signal val : std_logic_vector (2 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset ='1' then • val <= (others =>'0'); • elsif (clock'event and clock='1') then • val <= x & val (2 downto 1); • end if; • end process;

Behavioral description2 process • architecture behav of seq_rec is • signal val : std_logic_vector (2 downto 0); • constant SEQUENCE : • std_logic_vector (2 downto 0):= "010"; • begin • PSO: process (reset, clock) • begin • if reset ='1' then • val <= (others =>'0'); • elsif (clock'event and clock='1') then • val <= x & val (2 downto 1); • end if; • end process;

Behavioral description2 process(cont’d) • PO: process (val) • begin • if (val = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end process; • end behav;

Behavioral description2 process(cont’d) • PO: process (val) • begin • if (val = SEQUENCE) then • z <= '1'; • else • z <= '0'; • end if; • end process; • end behav;

Behavioral description system RT logic STG behavior structure physical

010 reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 Solution

Behavioral description system RT logic STG description2 process behavior structure physical

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process • architecture stg of seq_rec is • type STATE_SET is (S_R,S_0,S_01,S_010); • signal state : STATE_SET; • begin • PS: process (clock, reset) • begin • if reset = '1' then • state <= S_R; • elsif (clock'event and clock = '1') then

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process • architecture stg of seq_rec is • type STATE_SET is (S_R,S_0,S_01,S_010); • signal state : STATE_SET; • begin • PS: process (clock, reset) • begin • if reset = '1' then • state <= S_R; • elsif (clock'event and clock = '1') then

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process(cont’d) • case state is • when S_R => • if x ='0' then • state <= S_0; • when S_0 => • if x = '1' then • state <= S_01; • end if; • when S_01 => • if x = '0'then • state <= S_010; • else • state <= S_R; • end if;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process(cont’d) • case state is • when S_R => • if x ='0' then • state <= S_0; • when S_0 => • if x = '1' then • state <= S_01; • end if; • when S_01 => • if x = '0'then • state <= S_010; • else • state <= S_R; • end if;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process(cont’d) • case state is • when S_R => • if x ='0' then • state <= S_0; • when S_0 => • if x = '1' then • state <= S_01; • end if; • when S_01 => • if x = '0'then • state <= S_010; • else • state <= S_R; • end if;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process(cont’d) • when s_010 => • if x = '0' then • state <= S_0; • else • state <= S_01; • end if; • end case; • end if; • end process;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description2 process(cont’d) • PO: process (state) • begin • case state is • when S_010 => z <= '1'; • when others => z <= '0'; • end case; • end process; • end stg;

Binary encoding STG description2 process(cont’d) • architecture stg of seq_rec is • type STATE_SET is (S_R,S_0,S_01,S_010); • signal state : STATE_SET; • begin • PS: process (clock, reset) • begin • if reset = '1' then • state <= S_R; • elsif (clock'event and clock = '1') then

state encoding S_R 00 S_0 01 S_01 10 S_010 11 Binary encoding STG description2 process(cont’d) • architecture stg of seq_rec is • type STATE_SET is (S_R,S_0,S_01,S_010); • signal state : STATE_SET; • begin • PS: process (clock, reset) • begin • if reset = '1' then • state <= S_R; • elsif (clock'event and clock = '1') then Coded as: 0, 1, 2, 3 :

Binary encoding STG description2 process(cont’d)

One-hot encoding STG description2 process(cont’d)

Behavioral description system RT logic STG description1 process behavior structure physical

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description1 process • architecture stg of seq_rec is • type STATE_SET is (S_R,S_0,S_01,S_010); • signal state : STATE_SET; • begin • PS: process (clock, reset) • begin • if reset = '1' then • state <= S_R; • z <= '0'; • elsif (clock'event and clock = '1') then

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description1 process(cont’d) • case state is • when S_R => • if x ='0' then • state <= S_0; • -- z not specified, since in next state • -- it will be equal to the current one • end if; • when S_0 => • if x = '1' then • state <= S_01; • end if;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description1 process(cont’d) • case state is • when S_R => • if x ='0' then • state <= S_0; • -- z not specified, since in next state • -- it will be equal to the current one • end if; • when S_0 => • if x = '1' then • state <= S_01; • end if;

reset 1 0 R,0 0,0 0 1 0 1 0 01,0 010,1 1 STG description1 process(cont’d) • when S_01 => • if x = '0'then • state <= S_010; • z <= '1'; • else • state <= S_R; • end if;