Width Minimization In the Single-Electron Transistor Array Synthesis

Width Minimization In the Single-Electron Transistor Array Synthesis. Speaker: Chian Wei Liu Advisor: Dr. Chun-Yao Wang 2014/01/13. OUTLINE. Motivation Width minimization approach Discussion Experimental result Future work. M otivation.

Width Minimization In the Single-Electron Transistor Array Synthesis

E N D

Presentation Transcript

Width Minimization In the Single-Electron Transistor Array Synthesis Speaker: Chian Wei Liu Advisor: Dr. Chun-Yao Wang 2014/01/13

OUTLINE • Motivation • Width minimization approach • Discussion • Experimental result • Future work

Motivation • The previous work focuses on reducing the number of hexagons in SET arrays while the area is more related to the width. 1 1 -3 -2 -1 0 1 2 3 -3 -2 -1 0 1 2 3

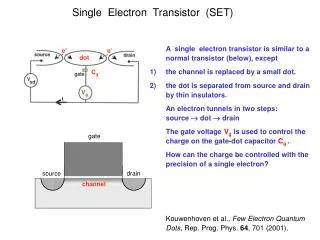

Problem Formulation • Given: • A Boolean circuit and its LTG network. • Objective: • Configuring the circuit into SET arrays result in the smaller width.

OUTLINE • Motivation • Width minimization approach • Discussion • Experimental result • Future work

Key Idea • Reducing numbers of product terms • Architecture relaxation • In the previous work, for simplification, they allow either (high, low) or (low, high) to appear in an SET array • For width minimization, we allow both (high, low) and (low, high) to appear in an SET array • Branch-then-Share collection

Width Minimization Approach • Product term computation from Threshold Networks • Branch-then-Share collection • Variable reordering • Architecture relaxation • Product term reordering

OUTLINE • Motivation • Width minimization approach • Discussion • Experimental result • Future work

Discussion • The tradeoff between the time and the area P1: 21001 P2: 20201 P3: 20212 P4: 21012 rechecking costs too much time

Discussion • Would the ladder-shape architecture makes the width smaller ? ?

OUTLINE • Motivation • Width minimization approach • Discussion • Experimental result • Future work

OUTLINE • Motivation • Width minimization approach • Discussion • Experimental result • Future work

Key Idea • Reducing numbers of product terms • Architecture relaxation • Branch-then-Share collection creation

Future work • Reordering variables according to the feature of the Branch-then-Share to creature more Branch-the-Share • If the EBL is not meaningful of width minimization, the product term reordering should make down the priority of the EBL • Proposing a new method of enhance expansion focusing on width minimization • Remap the nodes if the expansion occurs at the middle of the array