On reconfigurable Single-Electron Transistor Arrays Width Minimization

360 likes | 515 Vues

On reconfigurable Single-Electron Transistor Arrays Width Minimization. Speaker: Chain Wei Liu Advisor: Dr. Chun-Yao Wang 2 013/02/18. OUTLINE. Introduction Previous work Problem formulation Width optimization approach Future work. I ntroduction. current detector.

On reconfigurable Single-Electron Transistor Arrays Width Minimization

E N D

Presentation Transcript

On reconfigurable Single-Electron Transistor Arrays Width Minimization Speaker: Chain Wei Liu Advisor: Dr. Chun-Yao Wang 2013/02/18

OUTLINE • Introduction • Previous work • Problem formulation • Width optimization approach • Future work

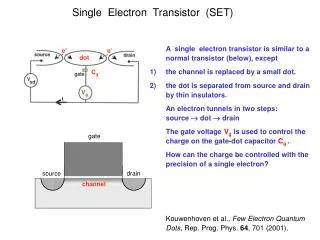

Introduction current detector • SET: Single-Electron Transistor • An SET array can be presented as a graph composed of hexagons • All sloping edges areconfigurable • short, open, active (high or low) • Active edges at the same row are controlled by a single variable 1

Example • An example of a XOR b: active high a active low short open b

Mapping constraint • Constraint-free • The decision of configuration direction depends on the location of node • Avoid creating incorrect mapping 0110 010- 11- -

Mapping constraint • Granularity constraint • Two edges are configured simultaneously • The combination of n.left and n.right, (n.left,n.right), must be one of (high, low), (low, high), (short, short),and (open, open), where n is a node in the SET array. 0110 010- 11- -

Mapping constraint • Fabric constraint • (high, low) and (low, high) cannot simultaneously appear in a row • In the previous work, for simplification, they allow only one of (high, low) and (low, high) to appear in an SET array • For width minimization, we allow both (high, low) and (low, high) to appear in an SET array

Example In the previous work Our approach 0110 010- 11- - • 0110 • 010- • 11- -

OUTLINE • Introduction • Previous work • Variable reordering • Product term reordering • Problem formulation • Width optimization approach • Future work

Previous Work current detector • BDD -> Product term -> SET array 0010 01-0 100- 11-- 0 1 1

Variable reordering • Variable preprocess • Move the variables with the same logic value among all product terms to the front • Share collection • Collect the pairs of product terms which have many shared edges

Share collection • Branch-and-Share • After the merging point, all the variables should be the same value • Case: (01,10), (1-,01), (0-,10) • Case: (0011,1100) ,(00-1,11-0) , (00--,11-0) ,… 001001 010001

Variable reordering • Reordering remaining variables • move the variables which have the maximal number of Max(#0,#1,#-) to the front on the premise of avoiding destroying share relation • If there is a tie, move the variable which has no don’t care bits • If there is a tie and all columns have don’t care bits, then move the variables in accordance with the original column ordering

Example abcdefg abcdefg abcdefg --110-111 --110-110 --1101101 --110-000 --1100001 --1010001 --00-0000 --110-111 --110-110 --1101101 --110-000 --1100001 --1010001 --00-0000 --110-111 --110-110 --1101101 --110-000 --1100001 --1010001 --00-0000 0: 001253453 1: 006511324 -: 770013000 Max: 776553454 abcefdg abcedfg --11011-1 --11011-0 --1101011 --11000-0 --1100001 --1010001 --00-0000 --11011-1 --11011-0 --1101011 --11000-0 --1100001 --1010001 --00-0000 --1101-11 --1101-10 --1101101 --1100-00 --1100001 --1010001 --00-0000

Product term reordering • Product term grouping • Expansion level prediction • Product term order determination

Product term grouping --11011-1 P1 --11011-0 P2 --1101011 P3 --11000-0 P4 --1100001 P5 --1010001 P6 --00-0000 P7 P1~P7 --1 --0 --11 P1~P6 --10 P7 --1100 --1101 P3 P4,P5 P1,P2 P1~P5 P6 --11011 --11010 label P1~P3 Leaf group

Expansion level prediction • Justify the don’t care value after grouping bits • In label • Scan bits from the end of the label and replace don’t care value as the first scanned bit value which is not don’t care bit. • Other bits • Replace don’t care value as the bit value (0 or 1) which is the maximum number in the label • If there is a tie, find the last bit of the label as the replacement value

Expansion level prediction • Predict the upper bound of expansion level for each product term • Predict expansion level by checking the last two bits of label and continuously scan the same logic value • 0111101 • 0110100 Expansion level:5 Expansion level:3 label

Product term order determination • Determine the product term order by expansion level, share collection and group relation • Priority: share collection > group relation > expansion level

Example --11011-1 P1 --11011-0 P2 --1101011 P3 --11000-0 P4 --1100001 P5 --1010001 P6 --00-0000 P7 P1~P7 --1 --0 --110 P1~P6 --10 P7 P1:9 P2:8 P3:6 --1100 --1101 P3 P1,P2 P4,P5 P4:9 P1~P5 P5:8 P6 P6:3 P7:9 --11011 --11010 label P1~P3 Leaf group

OUTLINE • Introduction • Previous work • Variable reordering • Product term reordering • Problem formulation • Width optimization approach • Future work

Problem formulation • Given: • A logic circuit • Objective: • An SET array architecture with smaller width

Key idea • Relax mapping constraint • More Branch-and Share can be used • Limiting expansion of the SET array

OUTLINE • Introduction • Previous work • Variable reordering • Product term reordering • Problem formulation • Width optimization approach • Future work

Share collection • Branch-and-Share • Two bits • (1,0)(0,1) (1,-)(0,1) (1,0)(0,-) (1,-)(0,-) (-,0)(-,1) • (1,1)(0,0) (1,-)(0,0) (1,1)(0,-) (1,-)(0,-) (-,1)(-,0) (high,low) (high,low) (high,low) (low,high)

Share collection • Branch-and-Share • Four bits

How to select Branch-and-Share • Scan product term from the top to the bottom • For each product term, count the number of Branch-and-Share • Choose the set of Branch-and-Share with maximum numbers • If there is a tie, choose the first one • Can not conflict with the selected Branch-and-Share

Determine the SET array architecture • The first row is always configured as (high,low) • When there is a Branch-and-share, determine the row structure to meet the Branch-and-share requirement • Other row structures are determined as the previous row structure if over half of variables changes their value • Otherwise, inverse the row structure

Example-variables reordering 110100 P1 1100-- P2 1111-- P3 111000 P4 11101- P5 110100 P1 1100-- P2 1111-- P3 111000 P4 11101- P5 110100 P1 1100-- P2 1111-- P3 111000 P4 11101- P5 Share collection

Example-analysis architecture 110100 P1 1100-- P2 1111-- P3 111000 P4 11101- P5 P1~P5 111 110 P3~P5 1110 1111 P1 P2 H,L L,H H,L L,H L,H H,L 110100 P1 110011 P2 111111 P3 111000 P4 111011 P5 P4 P5 P3

Example-product term reordering H,L L,H H,L L,H L,H H,L 110100 P1 110011 P2 111111 P3 111000 P4 111011 P5 P1~P5 111 110 P3~P5 1110 1111 P1 P2 P1: 4 P2: 3 P3: 3 P4: 4 P5: 5 P4 P5 P2->P3->P5->P4->P1 P3

Example-mapping result Previous work Width optimization approach Width=13 Width=9

Mapping processing • Dynamic swap • Only expand the direction of don’t care variables that benefit to us • If there is one product term has a chance to expand on another product term but is forbidden by invalid paths or lacking spaces due to the expanding direction of don’t care variables, change the direction of don’t care variables and check • Use cost function

OUTLINE • Introduction • Previous work • Variable reordering • Product term reordering • Problem formulation • Width optimization approach • Future work

Future work • Find a method to get a better order of Branch-and-Share to optimize width • Verify the new method which is proposedtoday • Trace code