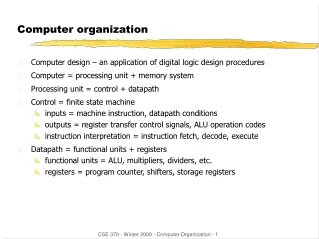

Computer Organization

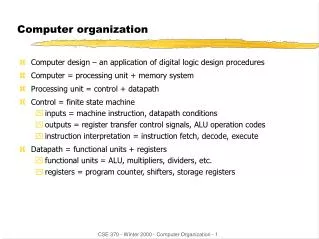

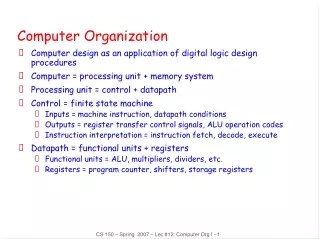

Explore concepts of binary addition, subtraction, overflow detection, bitwise complementers, controlled complementors, and efficient adder designs in computer organization. Learn about the Ripple Carry Adder, Parallel Adder, and Conditional Sum Adder. Understand various building blocks for memory and arithmetic operations.

Computer Organization

E N D

Presentation Transcript

Computer Organization Arithmetic and Memory Building Blocks

Si = (A B)C + (A B)C Recall x y + x y = x y Cout = CAB + CAB + CAB + CAB = AB(C + C) + C(AB+AB) = AB + C(A B) = AB + C(A B) = AB C(A B) Adder • Recall truth table for binary addition Cin Ai Bi Si Cout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 So Si = (A B) C

Basic Ripple Carry Adder • An n-bit unsigned integer ripple carry adder can be build from n Full Adders Full Adder

Basic Ripple Carry Adder (RCA) • Slow due to the ripple propagation of the carries

Overflow Detector • Overflow occurs whenever the carry-in into the sign bit is different from the carry-out from that sign bit • So we need an XOR at the output to indicate whether or not overflow has occurred

Ripple Carry Subtractor • We can subtract using addition • Form the 2’s comp of the subtrahend then add • So by adding hardware, we can do both addition and subtraction • We need a “mode” bit to tell us whether we are adding or subtracting

Bitwise controlled complementer • If mode m = 0, indicate addition, so S = A + B • If mode m = 1, indicate a subtraction, so S = A - B = A + B2 (my notation for 2’s comp) • Recall B2 = (bn-1 bn-2 … b0) + 1 • Neglect the “+1” for now and try to form B1

Bitwise controlled complementer bn-1 bn-2 … b0 Controlled Complimentor m b’n-1 b’n-2 … b’0 Where bi’ = bi, m=0 bi, m=1

m bi b’i 0 0 0 0 1 1 1 0 1 1 1 0 Bitwise controlled complementer • This can be done with XOR • For the “+1”, consider the following: • if m=0, we are adding • no complement • no “+1” • if m=1, we are subtracting • compliment • “+1” • Why not just add m? • Moreover, we can add m at the LSB carry-in!

RCA • The RCS’s are slow • very long “worst case” path • assumes a carry may have to propagate from the LSB FA all the way to the MSB FA • Why not compute each carry directly instead of having it propagate along? • Time more important than gate space • Gate space still important

Parallel adder • Recall a 4-bit sum: C4C3C2C1C0 A3A2A1A0 + B3B2B1B0 C4S3S2S1S0 Recall Si = (Ai Bi) Ci Ci = Ai-1Bi-1 Ci-1(Ai-1 Bi-1)

Conditional Sum Adder (CSA) • Let the true augend, addend, and sum bits be designated by Ai, Bi, and Si • Carries are indicated by Ci • Subscripts indicate bit position • Let superscripts indicate the assumption of the carry-in to bit position i: • Si1 = “1” carried into sum bit position i • Si0 = “0” carried into sum bit position i

CSA • S0(k) and S1(k) denote 2 provisional sums • each consists of multiple sections • k addend/augend bits per section • Then there are (n/k) sections for an n-bit addition • C0(k) and C1(k) are provisional carry sequences formed by carries out of all the sections in S0(k) and S1(k), respectively

CSA • Simultaneous addition are performed on all sections independently • Compute all of the S0, C0, S1, and C1 for each section independently • Select whether to use (Si0, Ci0) by the actual Ci-1 • Let k = 2j-1 for the jth step • Take log2n steps

CSA: Stage 1 bits 1 and 2 Notice C20(2) = C20 C21(2) = C21 Also notice that we don’t need C1 to decide (S20(2), C30(2)) or (S21(2), C31(2)) So we can compute these before we know C1 • If C1 == 0: • (S10(2), C20(2)) = (S10, C20) • If C20(2) == 0: • (S20(2), C30(2)) = (S20, C30) • Else [C20(2) == 1]: • (S20(2), C30(2)) = (S21, C31) • If C1 == 1: • (S11(2), C21(2)) = (S11, C21) • If C21(2) == 0: • (S21(2), C31(2)) = (S20, C30) • Else [C21(2) == 1]: • (S21(2), C31(2)) = (S21, C31)

CSA: Stage 1 bits 3 and 4 Notice C40(2) = C40 C41(2) = C41 Also notice that we don’t need C3 to decide (S40(2), C50(2)) or (S41(2), C51(2)) So we can compute these before we know C1 • If C3 == 0: • (S30(2), C40(2)) = (S30, C40) • If C40(2) == 0: • (S40(2), C50(2)) = (S40, C50) • Else [C40(2) == 1]: • (S40(2), C50(2)) = (S41, C51) • If C3 == 1: • (S31(2), C41(2)) = (S31, C41) • If C41(2) == 0: • (S41(2), C51(2)) = (S40, C50) • Else [C41(2) == 1]: • (S41(2), C51(2)) = (S41, C51)

CSA: Stage 1 bits 2 and 3 (simultaneously with bits 0, 1) • C20 and C21 both select new possibilities for (S20(2), C30(2)) and (S21(2), C31(2)) • If C20=0, we will select (S20(2), C30(2)) = (S20(1), C30(1)) • If C20=1, we will select (S20(2), C30(2)) = (S21(1), C31(1)) • If C21=0, we will select (S21(2), C31(2)) = (S20(1), C30(1)) • If C21=1, we will select (S21(2), C31(2)) = (S21(1), C31(1))

CSA: Stage 1 bits 2 and 3 continued • So we still have 4 values: S20(2), C30(2), S21(2), C31(2) • The choice will depend on whether C1 = 0 or 1 • Next stage will choose which one based on C1

CSA: Stage 1 following bit pairs • The CSA will work just like bits 2 and 3 for all subsequent bit pairs

CSA: Stage 2 bits 0-3 • The C1 output from stage 1 will select S1 = S10 or S11. • The C1 output from stage 1 will also select S2 = S20(2) or S21(2) • The C1 output from stage 1 will also select C3 = C30(2) or C31(2) • This C3 output will be used in stage 3 to select outputs for higher order bits

CSA: Higher stages, higher bits • We continue this setup for the higher-order bits

Ai Bi Ci Ci+10 Si0 Ci+11 Si1 0 0 0 0 0 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 CSA: Conditional Cell • We want to produce the conditional sums • Output does not depend on Ci

CSA: MPX • MPX’s for the CSA have n pairs of inputs • One line from each pair is selected by a single address line