Huffman Encoder Project

Huffman Encoder Project. Huffman Encoder Project. Howd - Zur Hung Eric Lai Wei Jie Lee Yu - Chiang Lee Design Manager: Jonathan P. Lee. Overall Project Objective : Design a Low Power Huffman Encoder. Final Presentation April 30 th , 2007. Agenda of Presentation.

Huffman Encoder Project

E N D

Presentation Transcript

Huffman Encoder Project Howd - Zur Hung Eric Lai Wei Jie Lee Yu - Chiang Lee Design Manager: Jonathan P. Lee Overall Project Objective:Design a Low Power Huffman Encoder Final Presentation April 30th, 2007

Agenda of Presentation • About Huffman Compression (Wei Jie) • Marketing (Wei Jie) • Project Description (Wei Jie) • Design Methodology (Randal) • Original Huffman Recipe (Randal) • Our Huffman Encoder (Randal) • Design Decisions (Randal) • Behavioral/Algorithmic Description (Eric) • Floorplan Evolution (Eric) • Layout (John) • Verification (Eric) • Issues Encountered (John) • Specifications (John) • Conclusions (John)

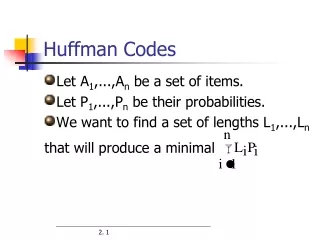

About Huffman • Huffman is a compression algorithm • Often used as a back-end to other compressions • Greedy algorithm

The Need for Compression • It is becoming a wireless world • Wireless bandwidth limited • Power is limited • COMPRESSION! • Reduce data size = Save power + time + bandwidth

Why Huffman? • Lossless • Statistical • David Huffman is the man! • Outdid Shannon-Fano coding

Project Description Our Huffman Encoderis a fast and power efficient solution to data compression with on-chip cache

Hardware compression out performs software based solution Small, affordable, and power efficient chip is perfect for portable devices Why Hardware?

Hardware Huffman Solution • Low power, compact, full-custom ASIC • Saves power,time, and system resources • Compress data packets on network cards • Cell phones, PDA, Laptop

Design Methodology • Understand the algorithm • Design functional blocks • Behavioral Verilog • Structural Verilog • Schematic • Layout • Simulations

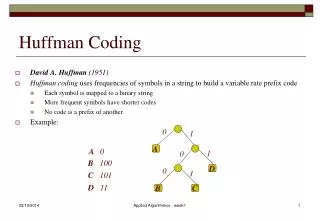

Specifics of Huffman a a b b c c d d e e 4 001 7 01 0001 2 1 0000 15 1 29 0 1 14 e 0 1 7 b 0 1 3 a 0 1 d c • Procedure • pre-scan data and count frequency • iteratively find least two frequent word and build a tree • encode word according to the final tree structure

Our Huffman a a a a a b b b b b c c c c c d d d d d e e e e e 7 14 4 29 4 7 29 14 7 7 3 29 14 2 7 1 7 3 14 29 15 29 15 15 15 0 0 0 0 0 0 1 1 1 0 0 0 2 0 2 2 0 0 3 0 4 4 4 4 0 001 01 1 01 1 0000 01 1 001 00 0 0000 000 1 • Procedure • pre-scan data, count frequency, and assign unique group number • iteratively find least two frequent word to update group number and encoding • finish encoding look up table

Design Decisions • 5-bit input word size • 16-bit frequency • Two SRAMs • Adders: 16-bit Carry Select Adders • Serial output • Control logic to shut down modules

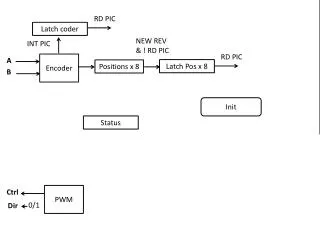

Behavioral / Algorithm Description turns off unused blocks to reduce power

Top countFreq Find2Freq Combine SRAMfreqGroup SRAMcodeLength serial output control

Verification: Verilog • Matched Verilog results with MATLAB results • Verified the successful compression of several test cases including parts of an image file:

Verification: Schematic • Vigorously tested each block • Combined them and encoded several words

Verification: Layout • Verified strong signal integrity • Buffered high fan-outs and long wires • Critical Path: 4.88 ns • All outputs of modules go through registers

Final Specifications • Number of Transistors : 23,322 • Area : 288.18 x 273.645 = 78859 μm2 • Density : 0.296 (transistors/μm2) • Aspect Ratio = 1:1.05 • Pin Count = 52 pins • Input : 5-bit data input, start, done, finish • Output : 36-bit treeOutput, treeReady, out, request, error • vdd!, gnd!, clk, reset • Final Clock Speed = 200 MHz

Final Specifications • Final result is up to1800 times faster than Java! (probably because it’s Java) • Compressed 640 bits of an image • Java results – 10 ms • Centrino 1.5 GHz • 512 RAM • Our hardware Huffman – 5.4 us • 1071 cycles

Issues Encountered • Bad estimate for original floorplan • Long SRAM simulation time • SRAM sense amp issue • Too much poly! • Cannot route through SRAM

Conclusions • Next Steps: • Scale up design • Better compression ratio • Higher throughput • Meeting of the Minds • HUFFMAN DECODER!!