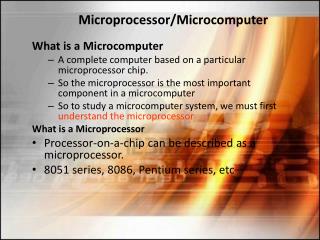

Microprocessor/Microcomputer

Microprocessor/Microcomputer. What is a Microcomputer A complete computer based on a particular microprocessor chip. So the microprocessor is the most important component in a microcomputer So to study a microcomputer system, we must first understand the microprocessor

Microprocessor/Microcomputer

E N D

Presentation Transcript

Microprocessor/Microcomputer What is a Microcomputer • A complete computer based on a particular microprocessor chip. • So the microprocessor is the most important component in a microcomputer • So to study a microcomputer system, we must first understand the microprocessor What is a Microprocessor • Processor-on-a-chip can be described as a microprocessor. • 8051 series, 8086, Pentium series, etc

Block diagram of a generic microcomputer system Hard Disk CD ROM RAM Data and address bus Keyboard, mouse Monitor, printer

Microprocessor based system uP with Control program motor sensor Output Input

The Intel 8086 Microprocessor • The 8086 is a popular device used in the early 70’s and 80’s and its architecture is simple and suitable for teaching computer architecture • Once we gain the basic concept of the 8086, we can then discuss the more advanced microprocessors • Many features found in 8086 are still being embedded in modern microprocessors but enhanced!

8086 Microprocessor • This is a 16-bit microprocessor chip manufactured by high-performance metal-oxide semiconductor (HMOS) technology • Circuitry on chip is approximately 29,000 transistors • Comes in a 40-pin package

Self test • Do you know what does it mean by 16-bit, 32-bit, or 64-bit processor? • How would you describe an Intel Core2 Duo CPU ?

Basic 8086 features • True 16-bit microprocessor with 16-bit internal and external data bus • The address bus and data bus are multiplexed??? • Multiplex – address and data share the same pin!! • A 20-bit address bus which allows access to 1 MB of memory. • Can address up to 64K byte-wide I/O ports • Or 32K word-wide ports (word = 16 bits) • Details regarding I/O ports will be discussed in the I/O System

Pins layout for 8086 A/D – address/data (address and data share the pins - multiplexed) Also pay attention to “active high” and “active low” signals

8086 Features • The 8086 has two modes – min. and max. • Min. mode – used as a typical microprocessor • Max. mode – use with multiple processors, usually for floating-point arithmetic) • The mode selection is via the MN/MX input

Block diagram for a simple computer system Display unit LCD What are the basic operations performance by a computer? memory CPU I/O Get instruction from memory Perform/Execute operation Get next instruction

What are the basic operations performed by a microprocessor? • Get instruction from memory • Perform/Execute operation • Get next instruction • So inside the microprocessor, it is organized into two units: Bus Interface Unit (BIU) and Execution Unit (EU). So that it can perform the above operations effectively

The 8086 Internal Architecture • The internal functions of the 8086 µP are divided between two separate processing units. They are the Bus Interfacing Unit (BIU) and the Execution Unit (EU). • The BIU is responsible for performing all bus operations, such as instruction fetching, reading and writing operands from/to memory, and inputting and outputting of data for peripherals. • The EU is responsible for executing instructions • The two units operate asynchronously so overlapping instruction fetch and execution is possible (what’s the advantage of this???)

Terminology • Program is stored in memory and consists of a sequence of instructions and some data • To execute an instruction it may require some operands • What is an operand? • Operand is the object that is being operated upon! • Example, in an instruction ADD A, B (A = A+B) • ADD (addition is the operation) • A and B are the operands

Bus Interfacing Unit (BIU) • The BIU is the 8086’s interface to the outside world (external memory). • The major task of BIU is to get “information” from the memory • Information includes data and instructions • How can we get data from memory????? • To access the memory, we need to issue an address (via the address bus) and then read the data (via the data bus) (Details of this mechanism will be discussed when we discuss the memory systems)

BIU • There is a full 16-bit bidirectional data bus and 20-bit address bus • It has the following functions: instruction fetch, instruction queueing, operand fetch and storage, and bus control. • It contains the segment registers, internal communication registers, instruction pointer, instruction object code queue, address summer (), and bus control logic.

How BIU and EU collaborate • What does a program consists of ??? • A program is a collection of instructions and data • BIU fetch an instruction from memory and put it in the queue and this is called instruction queue (refer to the block diagram) • EU fetches the instruction from the queue and executes • BIU and EU implements a pipeline (BIU->EU) and pre-fetch to optimize the performance

EU executes the instruction BIU Information coming from memory queue that can store 6 bytes of instructions Control to access the memory EU requests BIU to get operands BIU – EU Pipeline mechanism Note: there are 3 components in the pipeline

Pre-fetch concept • Pre-fetching is similar to what you do when you’re having a buffet dinner. • You collect different kinds of food from the buffet table, for example, you take the sashimi, roast beef, soup, and salad etc. • When you’re eating the salad, you have already pre-fetched the sashimi and the roast beef! If you do not pre-fetch then you take the salad first, go back to the table, eat your salad. When you finish the salad then you go and get some other food. • Why pre-fetching your food??????

Pre-fetch • Is pre-fetching in a buffet dinner exactly the same as the pre-fetching mechanism in a microprocessor? • The plate is equivalent to which component? • Is a big plate better than a small plate?

Pre-fetch by BIU • What’s pre-fetch???? • When the queue can store at least 2 bytes • EU is not requesting BIU to read or write operands from memory • BIU will look ahead in the program by prefetching the next sequential instruction • The prefetched instructions are held in the queue which is a FIFO (First-in-first-out) device • Two bytes are fetched (16-bit data bus) in a single memory cycle • EU will read one instruction byte from the output of the queue

Pre-fetch Queue EU int1a int1b int1a While EU is processing “int1a” Int2a and int2b have already been Pre-fetched int2b int2a int1b Memory

Pre-fetching by BIU • If the instruction queue is full and EU is not requesting access to operands in memory, the BIU does not perform any bus cycles – this is called idle states • When BIU is in the process of fetching an instruction when the EU requests its services then BIU first completes the instruction fetch bus cycle and then serves the EU

Components in the BIU • BIU is to read/write the memory • What is needed to access the memory??? • We need to generate an address and read/write the data • BIU contains a dedicated adder () which is used to generate the physical address of the memory location • Address is formed by adding an appended 16-bit segment address and a 16-bit offset address • Example: the physical address of the next instruction to be fetched is formed by combining the current contents of the code segment (CS) register (16-bit) and the current contents of the instruction pointer (IP) register (16-bit)

Generating the physical address • If CS (code segment) is 1005H • The IP is 5555H • What is the physical address? (how to determine the physical address?) • Point to consider: the address bus of the 8086 is 20-bit, the registers are 16-bit. Is it a problem???? • Consider the sum of two 16-bit values, what is the max. integer value represented by 16-bit.

Segment concept • 8086 can support up to 1M memory • Memory is divided into segments • Each segment is 64K • To access data inside a segment, we need to know the base address of a segment as well as the offset. • This is similar to a building, we can have room 10B, 11B etc. The floor is the base address and the letter ‘B’ is the offset

Segment in 8086 • Why segment mechanism is needed in 8086? • The address bus size (20-bit) > register size (16-bit) • Example: if the address bus is 4 bits then you can access 16 locations • If you can only output a 2-bit address from your register then what will happen? • Save components – can reduce the size of the registers • A segment is a 64Kbyte memory block

Segment concept • Segment analogy • It is similar to an estate • Instead of building a very tall building, we build smaller blocks • If you live in one of the smaller blocks then your address will have two components – the block number (segment) and the floor (offset)

Segment concept 1M A 64k segment How can we access locations within a segment ?????? A 64k segment

Segment Registers • The segment registers are used for accessing the memory • The 8086 address space is segmented into 64K-byte segments and just four segments can be active at a time. Because there are only 4 segment registers • In theory, how many segments can we have???? • Total memory 1M and segment is 64K so 1M/64K number of segment

The Segment concept So the real address (physical address) is = Base address (20 bits) + offset (16-bit) The Base address must be divisible by 16 so the last digit is equal to 0 and the ‘0’ is not stored so a 16-bit register can hold the rest of the address Memory (a segment) Real address Offset Base address (segment address)

Segment concept • For example: • FFFFEH is not divisible by 16 • FFFF0H is divisible by 16 • 12340H is also divisible by 16

Segment concept • The maximum value of a 16-bit value is FFFF (Hex), if two 16-bit values added together, such as FFFF (segment) + FFFF (offset), the result is 1FFFE (Hex) (physical) and it is only a 17-bit value and values from 1FFFFH to FFFFFH cannot be produced. As for a 20-bit pattern, it represents values from 00000H - FFFFFH • So in 8086, you cannot randomly assign a segment. The segment address must satisfy one condition, that is the base address must be divisible by 16. If a value is divisible by 16 and if we are using HEX (base 16) as the number system then the last digit of the value must be a ‘0’. • For example, the value in the segment register is 1234H and the offset is 20H then the physical address is 12340H + 20H = 12360H.

Segment concept • The segment concept analogy • If you are design the elevator for a very tall building, for example with 100 levels. How are you going to arrange the buttons if the elevator is able to reach all levels?

Execution Unit (EU) • The EU is responsible for decoding and executing all instructions. • What is decoding ? • The EU will see data such as 8B C3 (10001011 11010011) • Decoding is to carry out the proper operation according to the binary string (10001011 11010011) • 8B C3 is (MOV AX, BX) • After decoding, EU will perform the move (MOV) operation

Control signals Decoder Instruction 10101100 Decoding

Execution Unit (EU) (Cont’d) • EU consists of an ALU (Arithmetic and Logic Unit), status and control flags, eight general-purpose registers, temporary registers, and queue control logic • The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operand addresses if necessary, passes them to the BIU and requests it to perform the read or write bus cycles to memory or I/O, and performs the operation specified by the instruction on the operands. • During execution of the instruction, the EU tests the status and control flags and updates them based on the results of executing the instruction.

Functions of EU • ADD AX, 16 ; meaning add 16 to AX • Where AX is a register inside the CPU • If AX is 20 then after the operation it becomes 36 • For the above operation, do we need to fetch operand from memory? • 16 in the above operation is called an immediate • Immediate values are stored as part of an instruction and fetched together with the instruction • Now if it is ADD AX, X ; X is a variable • Do we need to fetch the operand X from memory?

Functions of EU • If the instruction queue is empty, the EU waits for the next instruction byte to be fetched and shifted to the top of the queue. • When the EU executes a branch or jump instruction, it transfers control to a location corresponding to another set of sequential instructions. Whenever this happens, the BIU automatically resets the queue and then begins to fetch instructions from this new location to refill the queue.

Summary • What is the pre-fetch concept? • What is a pipeline and its advantage? • What are functions performed by the BIU and EU • What is a multiplexed address/data bus • What is the segment concept

8086 Internal Registers • Registers are a very important component because they are used as a temporary storage, as well as storing the current status of the CPU. Contents of some registers indicate the memory locations to be fetched. • Registers are internal components that we can control with assembly language programming • 4 groups of 16-bit register • Instruction Pointer (IP) • Data Registers (4) • Pointers and Index Registers (4) • Segment Registers (4) • The Flag Register

Instruction Pointer (IP) • Identifies the location of the next instruction to be executed in the current code segment • IP contains an offset value not the physical address of the next instruction • Physical address = IP+CS (code segment register) • Every time an instruction word is fetched from memory, the BIU updates the values in IP (eg IP = IP+1) such that it points to the next sequential instruction word in memory

Data Registers • 4 general purpose data registers and are used for temporary storage of frequently used intermediate results. • This can improve the speed (why???) • Register can use either as 8-bit or 16-bit • Accumulator Register (AX: AH AL) • Base Register (BX: BH BL) • Count Register (CX: CH CL) • Data Register (DX: DH DL)

Data Registers • The general purpose data registers can be used for arithmetic or logic operations • For example, to carry out an addition: add ax, bx • The result is stored in ax and it is equal to the sum of values in ax and bx (in C, it is similar to ax+=bx) • For string instruction, the CX register is used to store a count value representing the number of bytes to be moved • All I/O operations require data that are to be input or output to be in the A register, while register DX holds the address of the I/O port

Segment Registers • The segment registers are used for accessing the memory • The 8086 address space is segmented into 64K-byte segments and just four segments can be active at a time. • In theory, how many segments can we have???? • The segment registers are used to select the active segments • Code Segment (CS) Register • CS identifies the starting address of the 64-K byte segment known as the code segment. Code segments of memory contain instructions of the program. • Data Segment (DS) Register • DS register identifies the starting location of the current data segment in memory. Data is stored in the data segment.

Segment Registers (Cont’d) • Stack Segment (SS) Register • SS register contains a logical address that identifies the starting location of the current stack segment in memory. Stack is used for temporary storage • Extra Segment (ES) Register • ES register identifies the extra segment usually used for data storage. • The segment registers store the base address of a segment. To determine the physical address, an offset is required. The index registers are used to store the offset value.