Generating 0% and 100% Duty Cycle with PWM Timers

This guide explains how to generate both 0% and 100% duty cycles using buffered or unbuffered PWM. To achieve a 0% duty cycle, configure the Output Compare register to $0000 and manage timer overflow conditions appropriately. For a 100% duty cycle, set the Output Compare register to match the Timer Mode (TMOD) value. The document details the implications of enabling and disabling certain bits in the Timer Channel Status and Control registers, allowing users to efficiently manipulate PWM duty cycles.

Generating 0% and 100% Duty Cycle with PWM Timers

E N D

Presentation Transcript

APPENDIX A: TIMER 0% and 100% Duty GENERATION

Generating 0% Duty Cycle • How do you generate a 0% duty cycle for either a buffered or unbuffered PWM? Set Output Compare register to $0000, right? • Output Compare and Timer Overflow would occur at same time • Timer Overflow takes precedence over Output Compare • Would produce 50% duty cycle PWM with a period twice the original • Answer: Disable timer counter toggle on overflow • Clear TOVx in TSCx • All future overflows will not effect output • Output compares will also have no effect • Continues to forcing output pin to same state

period #1 period #2 period #3 A B C D E Generating 0% Duty Cycle • Clearing TOVx at any time in period #1 will: • Disable toggle on overflow • Enabling 0% duty cycle in period #2 • Output compare will force output line low at time C • No change, forces to same state • Enabling the TOVx bit at any time in period #2 will: • Re-enable toggle on overflow • Reverting to normal PWM operation

Generating 100% Duty Cycle • How do you generate a 100% duty cycle for either a buffered or unbuffered PWM? Set Output Compare register equal to TMOD value • Same result as in 0% duty cycle • Answer: Use Channel Maximum

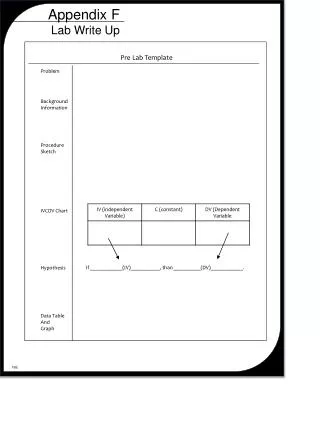

READ: CHxF TSCx CHxE MSxB MSxA ELSxB ELSxA TOVx CHxMAX WRITE: 0 RESET: 0 0 0 0 0 0 0 0 x = Channel number 0, 1, 2, etc. 100% Duty Cycle Selection • Timer Channel Status and Control Registers (TSC0 - TSC3) • Channel Max - 100% PWM duty cycle (CHxMAX) • Forces duty cycle to 100% • Takes effect in cycle after being set or cleared 1 = Enable 100 % duty cycle 0 = Disabled

period #1 period #2 period #3 A B C D E F Generating 100% Duty Cycle • Once CHxMAX is set • Next counter toggle overflow will occur • All subsequent output operations are disabled • Freezing output at 100% duty cycle • Setting CHxMAX at any time in period #1 enables 100% duty cycle in period #2 • Counter overflow toggle at B toggles output pin • All future toggle on overflows (D and F, etc) and output compares (C and E, etc) are disabled

period #1 period #2 period #3 D A B C E F Generating 100% Duty Cycle • Clear CHxMAX bit to resume normal PWM operation • Re-enables output compares and toggle on overflow • Next counter overflow will not toggle output • Clearing CHxMAX at any time in period #1 will enable normal PWM operation in period #2 • Counter overflow at B will not toggle output pin • Following counter overflows (times D, F) will toggle • Output compares force output low at times C and E