Advancements in Hierarchical Z-Buffer Techniques for 3D Graphics Hardware

This summary explores the innovative two-level Hierarchical Z-Buffer (HZ) system as detailed in the US Patent Application 2003/0151606 by Cheng-Hsien Chen and Chen-Yi Lee. Highlighting improvements such as a dual-level architecture that enhances access efficiency and memory management, it discusses features like Z caching, memory compression/decompression mechanisms, and replacement policies. This work provides valuable insights into the Z-buffering process, offering a foundation for future advancements in graphical rendering technologies and performance optimization in 3D graphics hardware.

Advancements in Hierarchical Z-Buffer Techniques for 3D Graphics Hardware

E N D

Presentation Transcript

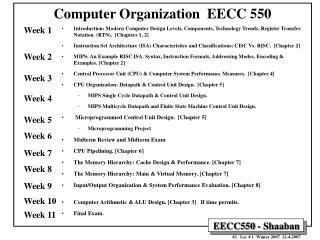

Status – Week 228 Victor Moya

Summary • Hierarchical Z-Buffer.

Hierarchical Z-Buffer • Two Level Hierarchical Z-Buffer for 3D Graphics Hardware. Cheng-Hsien Chen, Chen-Yi Lee. • System, Method and Apparatus for Multi-Level Hierarchical Z Buffering. US Patent Application 2003/0151606.

Hierarchical Z-Buffer PA CLIP RAST INT PS FTEST HZ HZ ZTEST

Hierarchical Z-Buffer HZ MEM MERGE LOGIC COMBINING CACHE Z CACHE DECODE ENCODE MEMORY (Z-BUFFER)

Hierarchical Buffer • Model from ATI patent application. • See also two other ATI patents about early implementations of the HZ. • Two level HZ. • but only one used? • Early Z access is performed in two phases: • access to the HZ L2. • if passes, access the Z cache. • if miss, access memory (fetch new Z cache line).

Hierarchical Z-Buffer • Z Cache • small lines? 32 bit per pixel, 4 pixels per line? • data is compressed in the Z-Buffer. • decode/decompress at line fetch. • encode/compress at line evict. • compress mechanism is also used to calculate the farthest Z value in the line. • size? • replacement policy?

Hierarchical Z-Buffer • HZ Memory • each position stores the farthest Z value in a NxM tile of the original Z Buffer. • data precission? 8 bits? 16 bits? 32 bits? • combine cache to build the tile farthest value. • number of HZ levels? • L1 on die, L2 on cache/memory.

Hierarchical Z-Buffer • HZ memory • combining cache size? • replacement policy? FIFO? • update mechanism

Hierarchical Z-Buffer • HZ Memory • size? • Example: • 8x8 tiles • 8 bits per value • 2048x2048 resolution • 64KB • a second level can be implemented using pointers. • LARGE!

Hierarchical Z-Buffer Z write HZ Buffer Bit-mask Cache

Hierarchical Z-Buffer TMPZ COVERAGE MASK COVERAGE?

Hierarchical Z-Buffer • Light weight Z-Buffer? • HZ Buffer: • 2 bit pointer (L2 HZ). • 4 x 8 bit Z values (L1 HZ). • ~49 KB for 1024x768. • HZ test per primitive. • HZ test per fragment.

Hierarchical Z-Buffer • Bit-mask cache: • builds HZ blocks. • holds the current farthest Z for the block. • 1 bit per block pixel: covered. • FIFO replacing policy. • if full block covered update HZ buffer.

Hierarchical Z-Buffer cull access HZ discard passes hit cull access Z Cache test discard pass pass miss Access memory Replace test

Hierarchical Z-Buffer fragment Triangle Traversal Interpolator test Z test? Hierarchical Z Z Cache HZ TEST BOXES Memor Controller

Hierarchical Z Buffer Z TEST AND Z AND HZ UPDATE BOXES fragment fragment Z test Z cache Memory Controller Hierarchical Z

Cache simulation c1 c2 c3 c4 c5 accc3 box1 acc1 acc2 res1 res2 res3 box2 acc1 acc2 acc3 Latency 2 Throughput 1 Box2 = cache

Cache simulation c1 c2 c3 c4 c5 acc2 accc3 box1 acc1 res1 res2 res3 Box1 => included cache Latency 1 cycle Throughput 1

Cache simulation • Use always 2+ cycle access caches? • Use always in-box caches? • Shared cache?