SoC Clock Synchronizers Project

250 likes | 367 Vues

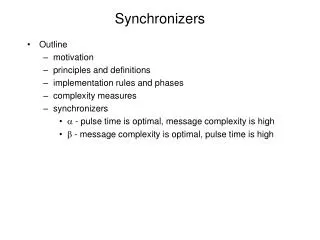

This presentation focuses on the synchronization challenges faced in large chip designs with multiple clock domains. We discuss the problems of data transfer between different clock domains, the risks of metastability, and synchronization failure probability. The project motivation highlights the increasing frequency of synchronization issues in the industry, necessitating better solutions. Various synchronization classifications and solutions, including mesochronous, plesiochronous, and asynchronous methods, will be explored. Our goals include comparing these methods based on latency, area, power, and simplicity.

SoC Clock Synchronizers Project

E N D

Presentation Transcript

SoC Clock Synchronizers Project Characterization Presentation Elihai Maicas Harel Mechlovitz

Presentation Agenda: • The synchronization problem • Project motivation • Synchronization classifications • Various solutions • Our goals • Timeline

The synchnization problem • Large chips have multiple clock domains because: • Chip interfaces with several unrelated blocks • Chip has inner IPs that require different frequency • Chip size is growing, what makes it hard to design one LARGE single clock • And more…

The synchnization problem • Example: A communication Hub

The synchnization problem • When spreading out the problem, it comes to transfer data from transmitter to receiver: • Given that ckA and ckB are not from the same clock domain, there is a probability that the receiver won’t sample the data correctly • Metastability • ts/th issues • Duplicate / dropped samples

The synchnization problem • What is the probability of this unfortunate situation to occur ? • In general, the probability of synchronization failure can be calculated as follows:P(failure) = P(enter metastable state) · P(still in metastable state after tw)

The synchnization problem • Flip-flop can enter a metastable state, when its data input D changes the state during the aperture time or sampling window of the flip-flop • Probability of an input transition to occur during the sampling window is computed by dividing the apeture time ta by the clock period tcy

Project motivation • Sync problems become more and more frequent in the industry • Common knowledge is quite insufficient • Solutions are not well categorized • Too little do we know about the various solutions • Common synchronization mistakes • Some of the solutions were never looked at closely for proper correctness checking

Synchronization classification • We can classify different synchronization problems to number of groups:

Synchronization classifications • Mesochronous • Phase difference stays constant • We could have a problem if clkB came too fast after clkA (not allowing proper ts), or too slow (not allowing th)

Synchronization classifications • Plesiochronous • Phase difference drifts • ∆f< ε • Other • Every few cycles we might have a sync problem needs to be solved

Synchronization classifications • Periodic • Events are periodic, therefore enables prediction • The sychronizer can detect a conflict enough time a head for the resualt to be ready on time

Synchronization classifications • Asynchronous • Communication between two asynchronic blocks • Sampling asynchronic signals (real-world input devices) for a synchronized block • Synchronization is required when the outputs or output events depend on the order in which input events are received • Asynchronous design is sometimes selected for eliminating the need for synchronization

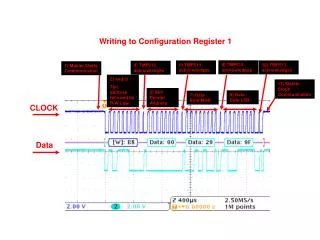

Various solutions • General solution • The Two-FF synchronizer AKA Brute-Force synchronizer • The first flop samples signal A • AW has a high probability of being in a metastable state • The second flop samples AW after a large waiting time allowing the metastable state to decay

Various solutions • Mesochronous solution • By delaying the clock with the actual phase difference, one of the registers will sample correctly

Various solutions • Plesiochronous solution • Using FIFO synchronizer, we can keep all timing needed for right sample

Various solutions • Periodic solution • Using prediction for shorter latency • Result (unsafe signal) is ready by the time input arrives

Various solutions • Asynchronous solution • Both clocks are aperiodic • Advantages • Lower probability of synchronization failure • Inherent flow-control

Our goals • Our main goal is to compare between various synchronization methods, with the following criteria: • Latency • Area • Power • Simplicity • Plug-n-play • Categorize the various solutions and give certain parameters for the choosing process of a synchronizer

Our goals • In addition, we will check correctness of above circuits with the following circuit: