Sequential Logic

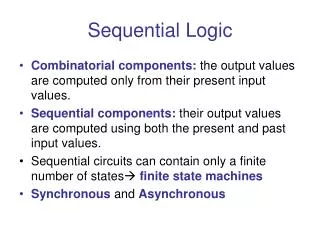

Sequential Logic. Latches and Flip-Flops. Sequential Logic Circuits. The output of sequential logic circuits depends on the past history of the state of the outputs. Therefore, it incorporate a memory element (circuits must remember the past states of their outputs).

Sequential Logic

E N D

Presentation Transcript

Sequential Logic Latches and Flip-Flops

Sequential Logic Circuits • The output of sequential logic circuits depends on the past history of the state of the outputs. • Therefore, it incorporate a memory element (circuits must remember the past states of their outputs). • Main characteristic of these circuits feedback • An output logic level is treated just like another input to the circuit.

Sequential Logic Circuits • Latches • Flip-flops

The S-R (SET-RESET) Latch Negative-OR equivalent of the NAND gate \S-\R latch

Flip-Flops • Flip-flops are synchronous bistable devices. • Synchronous means that the output changes state only at a specified point on the triggering input called the clock (CLK). • Changes in the output occur in synchronization with the clock.

Edge-Triggered JK-FF • JK-FF is versatile and is a widely used type of flip-flop. • The functioning of the JK-FF is identical to that of the SR-FF in the SET, RESET, and NC. • The difference is that the JK-FF has NO invalid state as does the SR-FF.

Asynchronous Preset and Clear Inputs • Most IC flip-flops have asynchronous inputs. • These are inputs that affect the state of the FF independent of the clock. • Preset (PRE) or direct set (SD) • Clear (CLR) or direct reset (RD) Logic symbol for a J-K flip-flop active-LOW preset and clear inputs.

Edge-triggered JK-FF with PRE and CLR Toggle mode example

Flip-Flop Applications • Parallel data storage

Flip-Flop Applications • Frequency division

Flip-Flop Applications • Frequency division

Flip-Flop Applications • Counting

Flip-Flop Applications • Counting