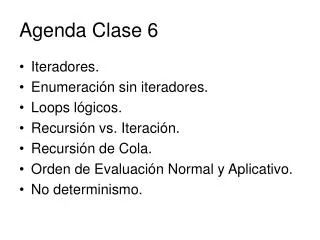

CLASE 6

CLASE 6. SE RECOMIENDA MIRAR LOS SIGUIENTES ENLACES. http:// www.virtual.unal.edu.co/cursos/ingenieria/2000477/index.html http://www.teahlab.com / http://medusa.unimet.edu.ve/sistemas/bpis03/clases.htm. NIVELES DE ACTIVACION. Señales activa en alto :

CLASE 6

E N D

Presentation Transcript

SE RECOMIENDA MIRAR LOS SIGUIENTES ENLACES • http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/index.html • http://www.teahlab.com/ • http://medusa.unimet.edu.ve/sistemas/bpis03/clases.htm

NIVELES DE ACTIVACION • Señales activa en alto: • Una señal es activa en alto cuando el nivel de activación ya sea en la entrada o en la salida (o en ambas) es ALTO o 1. • Cuando una línea de entrada o salida en un circuito no tiene circulo se dice que es activa en alto. • Señales activa en bajo: • Cuando una línea de entrada o salida en un circuito tiene circulo se dice que es activa en bajo. • Una señal es activa en alto cuando el nivel de activación ya sea en la entrada o en la salida (o en ambas) es BAJO o 0.

NIVELES DE ACTIVACION • Dado el circuito integrado del 74LS151 (Multiplexor 8:1). Cuales son las salidas (W y Y) cuando: • La entrada STROBE esta en ‘01, las líneas CBA están en ‘101’, las entradas D0-D5 están en ‘1’ y el resto esta en cero. • La entrada STROBE esta en ‘0’, las líneas CBA están en ‘101’, las entradas D0-D5 están en ‘1’ y el resto esta en cero.

RESUMEN DISPOSITIVOS MSI VISTOS HASTA EL MOMENTO Demultiplexor Multiplexor out 0 out 1 out 2 out 3 in 0 out 4 In Demux n:1 in 1 out 5 in 2 out 6 in 3 out 7 in 4 out 8 Out Mux n:1 … in 5 in 6 out n in 7 log2(n) in 8 … in n Sel log2(n) Sel

RESUMEN DISPOSITIVOS MSI VISTOS HASTA EL MOMENTO Decodificador Codificador A0 A1 A2 AN-1 O0 O1 O2 OM-1 decodificador A0 A1A2 AM-1 Codificador O0 O1 O2 ON-1 any M > N N > M

MULTIPLEXORES • Que hemos visto hasta el momento: • Multiplexores 2:1, 4:1, 8:1, 16:1. • Multiplexores comerciales: 74157, 74151. • Multiplexores en cascada: Formación de un multiplexor grande a partir de unos mas pequeños. • Implementación de funciones lógicas de n variables usando multiplexores y . • Mirar la siguiente URL: • http://medusa.unimet.edu.ve/sistemas/bpis03/guiasnuevas/guia9.html

DEMULTIPLEXORES • Que hemos visto hasta el momento: • La función del Demultiplexor es complementaria a la del multiplexor. • Algunos casos de multiplexores: 8:1, 4:1 y 2:1 entre otros. • Algunos demultiplexores comerciales: • Dual 1:4 demux : 74156,74139. • Demux 3:8: 74138. • Demux 1:16:74154, 74159. • Mirar la siguiente URL: • http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030601.htm

CODIFICADORES • Que hemos visto hasta el momento: • Realiza conversión de código. • El numero de entradas es mayor que el numero de salidas. (M > N). • Codificador binario ( a n): Algunos casos: 2:1, 4:1 y 8:1 entre otros. En estos solo una entrada estará activa y la salida será el código binario asociado a esta. • Mirar la siguiente URL: • http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030601.htm

CODIFICADORES CON PRIORIDAD Los codificadores de prioridad seleccionan la entrada de mayor prioridad cuando se presentan varias entradas activas simultáneamente. Codificador 8:3 con prioridad Si se activan varias entradas la mas prioritaria es la mas alta. Activación en bajo

CODIFICADORES Además de los codificadores binarios existen otro tipo de codificadores entre estos se encuentran. Codificador decimal a BCD Ver la siguiente URL: http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030502.htm

DECODIFICADORES • Que hemos visto hasta el momento: • Realiza conversión de código. • El numero de salidas es mayor que el numero de entradas. • Decodificador binario (n a): 4:2, 8:3, 16:4 entre otros. • Se pueden implementar funciones lógicas haciendo uso de decodificadores. • Es posible formar un decodificador mas grande a partir de otros mas pequeños. • Mirar la siguiente URL: • http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030601.htm

DECODIFICADORES • Además de los decodificadores binarios existen otro tipo de decodificadores: • Decodificador binario a decimal (7442). • Decodificador BCD a 7 segmentos (7446/7447). Ver la siguiente URL: http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030301.htm

USO DEL ENABLE • Todo circuito posee una señal para habilitar o deshabilitar su funcionamiento normal. Esta señal es conocida como señal de Enableo Strobe. • La implementación de esta señal se suele realizar empleando compuertas AND. • La señal de habilitación es aquella que cuando toma el valor de ‘1’ permite que la otra señal pase a la salida, sin embargo cuando toma el valor de ‘0’ hace que la salida sea ‘0’.

CIRCUITOS DE ENABLE/DISABLE • Diseñe un circuito que permita que una señal pase a la salida solo cuando las señales de control B y C estén en ALTO, de otro modo la salida deberá permanecer en BAJO. • Diseñe un circuito lógico que permita que una señal pase a la salida solo cuando una, pero no ambas, de las entradas de control son ALTAS. De otro modo la salida deberá permanecer siempre en ALTO.

CIRCUITOS DE MERGING E INVERSION • La compuerta OR realiza la función de merging de una señal. Esto es lleva la salida a alto cuando una de las señales se encuentre en una sin importar el estado de la otra. • La compuerta XOR realiza la función de inversión, esto de tal manera que cuando una de las señales esta en ‘0’ la salida es la otra señal, pero cuando esta en ‘1’ la salida será la otra señal invertida.

EJERCICIOS DE REPASO • Diseñar un codificador binario de 4 a 2 con prioridad, enable y salidas activas en bajo. • Diseñar un decodificador bcd a 7 segmentos para display de ánodo común. • Diseñar un multiplexor 4 a 1 con enable activo en bajo. • Diseñar un demultiplexor 1 a 4 con selección activa en bajo. • Diseñar un multiplexor 2 a 1 de líneas de datos de 8 bits.

TRI-STATES • Anteriormente vimos que todos los circuitos tenían dos posibles estados, ALTO (‘1’) o BAJO (‘0’). • Sin embargo existen casos en los cuales se desearía la conexión por ejemplo de dos salidas a una misma señal. 0 BANG 1 • Para solucionar problemas como el anterior es necesario que solo se direccione una salida en un momento especifico y es aquí donde aparece el buffer triestado (tri-state).

TRI-STATES • Un tri-state es un circuito digital que posee tres estados: ALTO (‘1’), BAJO (‘0’) y ALTA IMPEDANCIA (‘Z’). C = ‘Z’ si B = ‘0’ C = A si B=‘1’ Señal de control (habilitación): Cuando B esta abierto y C esta en alta impedancia ‘Z’. • Tipos de buffer triestados:

USO DE LOS TRI-STATES • Permite que diferentes fuentes (salidas) compartan un mismo bus. • Permiten manejar puertos de salida bidireccionales en circuitos integrados

COMPARADORES DE MAGNITUG • Circuitos digitales que realizan la comparación de dos entradas. • La comparación entre las entradas implica la evaluación de tres posibles condiciones: • Mayor que (>). • Menor que (<). • Igual que (=). • Los otros casos de comparación son complementarios a los anteriores asi: • es el complemento de . • es el complemento de . • es el complemento de .

COMPARADORES DE DOS NUMEROS SIN SIGNO • Comparador para números sin signo de 2 bits • Las entradas son dos números sin signo A () y B (). • G = 1 cuando A > B y G = 0 cuando A B. • L = 1 cuando A <B y L = 0 cuando A B. • L = 0 y G = 0 entonces A B.

COMPARADORES DE DOS NUMEROS SIN SIGNO • Comparador para números sin signo de 4 bits • Las entradas son dos números sin signo de 4 bits A () y B (). • El circuito para comparar dos números de n bit tiene entradas en la tabla de verdad. Así, según lo anterior, realizar la tabla de verdad para este caso seria bastante engorroso ya que esta tendría 65536 filas. • Aprovechando la regularidad que puede presentar la función digital se puede deducir mediante una seria de pasos el circuito digital asociado. Procedimiento Sean A y B dos números de 4 bits Ambos números son iguales si todos los pares de dígitos significativos son iguales, esto es ,…, . Expresando esto como una función de equivalencia se tiene que: ’’ 0,1,2,3

COMPARADORES DE DOS NUMEROS SIN SIGNO A y B son iguales por lo tanto si todas las son ‘1’ lo cual dicta una operación AND entre estas variables: Para determinar si A es mayor o menor que B se inspeccionan las magnitudes relativas de los pares de dígitos principiando desde la posición mas significativa. Si los dos dígitos son iguales, el par de dígitos de la siguiente posición mas baja se comparan. Esta comparación continua hasta que se alcanza un par de dígitos desiguales. Si el digito correspondiente de A es 1 y el de B es 0, se concluye que A > B si los valores de los dígitos son los opuestos la conclusión es que B > A. Esto expresado en forma lógica es:

COMPARADORES DE DOS NUMEROS SIN SIGNO A continuación se muestra el circuito digital asociado:

COMPARADORES DE DOS NUMEROS SIN SIGNO Comparador para números sin signo de n bits Es posible formar un comparador de n bits por medio de la conexión en cascada o en paralelo de comparadores de 1 bit.

COMPARADORES DE DOS NUMEROS SIN SIGNO Comparador para números sin signo de n bits Es posible formar un comparador de n bits por medio de la conexión en cascada o en paralelo de comparadores de 2 bit.

SUMADORES Semisumador (Half adder) • El Semi-Sumador o Half-Adder (HA) es un dispositivo que efectúa la suma de 2 números (A y B) de 1 bit. • Se denomina semi-sumador (HA) porque solo considera el acarreo de salida (Cout).

SUMADORES Sumador completo (full adder) • El sumador completo o Full-Adder (FA) suma 2 números (A y B) de 1 con un acarreo de entrada Cin. • Cin puede ser un bit de acarreo que resulte de otra suma.

RESTADOR Restador medio • El sumador completo o Full-Adder (FA) suma 2 números (A y B) de 1 con un acarreo de entrada Cin. • Las entradas del circuito son el minuendo (A) y el sustraendo (B) y las salidas son la diferencia (D) y el préstamo de salida (P).

RESTADOR Restador completo • El Restador completo realiza la resta entre dos bits, considerando que se ha prestado un 1 de un estado menos significativo. • Las entradas A, B y Cdenotan el minuendo, el sustraendo y el bit prestado. Las salidas D y P representan a la diferencia y el préstamo.

SUMADOR DE N BITS ¿Y si se desea sumar datos de 2, 4, 6 ó 8 bits? Sin tener que hacer tablas de verdad? Una opción puede ser conectar en cascada varios sumadores completos de datos de 1 bit, así:

SUMADOR RESTADOR • Se parte de que la resta (A-B) es una suma con el operador B complementado a dos (A+[-B]). • Un sumador/restador es capaz de realizar las dos operaciones mediante una línea de control (S). A B Cout S Sumador/Restador F

SUMADOR RESTADOR • Recordemos que la compuerta XOR puede servir como inversor según el valor de una de las entradas:

UNIDAD ARITMETICO LOGICA (ALU) • Una unidad aritmética lógica puede realizar un conjunto de operaciones aritméticas básicas y un conjunto de operaciones lógicas, a través de líneas de selección. • Las cuatro entradas de A se combinan con las de B generando una operación de salida de cuatro bits en F. La entrada de selección de modo S2distingue entre las operaciones aritméticas y lógicas. Las entradas de selección S0 y S1determinan la operación aritmética o lógica. Ver la siguiente URL: http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/031201.htm