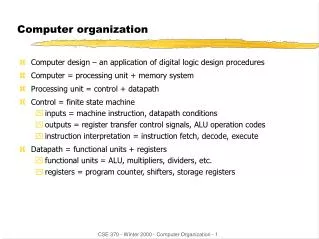

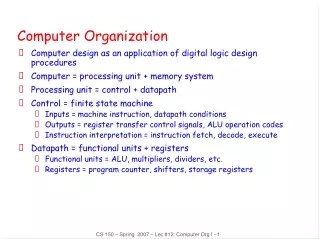

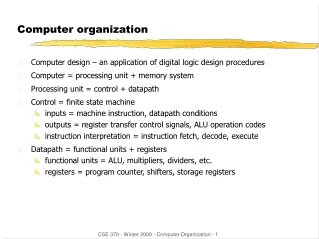

Computer Organization

This document provides a comprehensive overview of register transfer operations and bus design principles as discussed in Section 11.3 of Katz’s textbook. It covers in-class activities, memory address operations, ALU interactions, and control signals necessary for effective data flow in computational systems. The focus is on the transition from single bus designs to more complex systems involving multiple buses to enhance parallelism. Understanding these concepts is essential for successful instruction execution and memory management in computer architecture.

Computer Organization

E N D

Presentation Transcript

Computer Organization • Today: • First Hour: Computer Organization • Section 11.3 of Katz’s Textbook • In-class Activity #1 • Second Hour: Test Review

Register Transfer Operations Single Bus Design Register transfer operations: PC BUS IR BUS AC BUS MBR BUS ALU Result BUS BUS PC BUS IR BUS AC BUS MBR BUS ALU B BUS MAR AC ALU A (hardwired) Note, the BUS is treated just like a register

More Realistic Datapath Unit Three Bus Design — Supports more parallelism Memory Bus (MBUS) Result Bus (RBUS) Address Bus (ABUS) Single bus replaced by three busses:

RBUS MBUS AC A B Memory N bits wide 2M words Memory Address ALU MAR S ABUS IR PC MBUS We simplified our datapath further by assuming that MBR is inside the memory system itself and MBUS has two branches. Add Memory Every device in this diagram has control signals that must be operated.

Control Flow Data Flow Add Control RBUS The control unit is a finite state machine (FSM). Every bit of the Instruction Register (IR), every other register’s OE and LOAD signals, every control input and flag output of the ALU, and every memory control signal is either an input or an output of the control unit. (Shown in red) MBUS AC A B Memory N bits wide 2M words Memory Address ALU FSM MAR S ABUS Opcode IR PC MBUS Reality Note #1:The control unit FSM is huge compared to the FSM examples that we’ve seen thus far!! Reality Note #2: The diagram above is extremely simplified compared to a real processor

OPCODE OPERAND SPECIFIER Instruction Format How does it work? (1) Let's trace an instruction: AC AC + Mem<address> Store Path Load Path AC 1. Instruction Fetch: Move PC to MAR Initiate a memory read sequence Move data from memory to IR A B Memory N bits wide Memory 2M words Address ALU FSM MAR S Opcode IR PC 2. Instruction Decode: Opcode bits of IR are input to control FSM Rest of IR bits encode the operand address Instruction Path 3. Operand Fetch: Move operand address from IR to MAR Initiate a memory read sequence

OPCODE OPERAND SPECIFIER Instruction Format How does it work? (2) Let us trace an instruction: AC AC + Mem<address> Store Path Load Path AC 4. Instruction Execute: Data available on load path Move data to ALU input Configure ALU to perform ADD operation Move result S to AC A B Memory N bits wide Memory 2Mwords Address ALU FSM MAR S Opcode IR PC Instruction Path 5. Housekeeping: Update PC to point at next instruction

The Control Unit What the Control unit is doing: Transfers data from one register to another Asserts appropriate control signals We can think about the control unit most easily in terms of a series of register transfers, using a programming-like notation Register transfer notation - A way to represent the detailed implementation of register transfer operations

Instruction fetch: PC MAR; -- move PC to MAR Memory Read; -- assert Memory READ signal Memory IR; -- load IR from Memory Instruction Decode: IF IR<op code> = ADD_FROM_MEMORY THEN Operand fetch: IR<addr> MAR; -- move operand addr to MAR Memory Read; -- assert Memory READ signal Memory ALU B; -- gate Memory to ALU B AC ALU A; -- gate AC to ALU A ALU ADD; -- instruct ALU to perform ADD ALU S AC; -- gate ALU result to AC Instruction Execution: Housekeeping: PC+1 PC; -- increment PC Register Transfer Notation Register to Register moves Assert Control Signal

Micro-Operations Instruction Fetch Instruction fetch: PC ABUS; ABUS MAR; 1 Read/Write*; MBR MBUS; MBUS IR; Instruction Decode: IF IR<OpCode> = LOAD_FROM_MEMORY THEN Operand fetch: IR<addr> MAR; 1 Read/Write*; MBR MBUS; MBUS ALU B; ALU PASS B; ALU Result RBUS; RBUS AC; Instruction Execution: Housekeeping: PC+1 PC;

Micro-operations One register transfer operation may be several micro-operations Some operations are directly implemented by functional units: e.g., ADD, Pass B, 0 PC, PC + 1 PC Some others require multiple control operations: e.g., PC MAR implemented as PC ABUS and ABUS MAR

Control Flow Data Flow Do Activity #1 Now RBUS MBUS AC A B Memory N bits wide 2M words Memory Address ALU FSM MAR S ABUS Opcode IR PC MBUS

RETAIN THE LAST PAGE(S) (#3 onwards)!! • For Next Class: • Bring Huang 68HC11 Textbook • Required Reading: • Chap 1 of the Huang 68HC11 book • This reading is necessary for getting points in the Studio Activity!