Xbox 360 Architecture

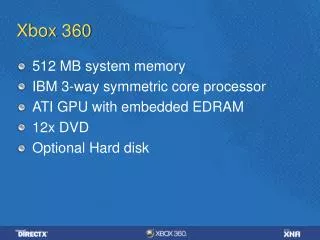

This overview discusses the architectural intricacies of the Xbox 360, focusing on its computational capabilities, core design decisions, and trade-offs. Key aspects include the PowerPC core's two-way set-associative cache, SIMD vector units, and multiplayer support through shared L2 cache. The design emphasizes cost-effectiveness, reduced latency, and adaptable workload management. It also explores streaming techniques for managing data without impacting cache performance, making the Xbox 360 a benchmark in gaming technology innovation.

Xbox 360 Architecture

E N D

Presentation Transcript

Xbox 360Architecture Presenter: Ataç Deniz Oral Date: 30/11/06

Overview • The Xbox • What kind of computation? • Architectural details • Decisions / Trade-offs • Conclusion • Discussion

The Xbox Photos taken from:http://www.xbox-scene.com

Computation • Decompression kernel • Game World Geometry • Data streaming • also • AI software • Audio synthesis

Why not use a PC? ●Dot product implementation ●Support for D3D formats Picture taken from: http://www.hotchips.org/archives/hc17/3_Tue/HC17.S8/HC17.S8T4.pdf

IBM PowerPC core 4 KB two-way set-associative BHT SIMD Vector unit Floating Point Unit Fixed Point Unit Load/Store Unit

Decisions / Trade Offs • Why multiple cores? (CMP versus SMP) • Cost-effective! • Enables shared L2 implementation (therefore reduces communication latency)

Decisions / Trade Offs (cont.) • Shared L2 Cache • To adapt to varying workloads • i.e. Scene management vs. audio processing

Decisions / Trade Offs (cont.) • In-order instruction issuance cores • Simplifies logic Reduced die area Reduced cost and power consumption • Out-of-order issuance requires • Additional pipeline stages to meet clock period timing • Rename registers and completion queues • In-order instruction execution • Claimed to be justified by two SMT (Symmetric MultiThreading) hardware threads per core

Computation • Decompression kernel • Game World Geometry • Data streaming

CPU Data StreamingWrite Streaming • Enable data streaming • But do not thrash private cache or shared cache • Write-through L1 caches

CPU Data StreamingWrite Streaming • Enable data streaming • But do not thrash private cache or shared cache • Write-through L1 caches • Uncached write gathering buffers in shared L2 for each core (for later dumping to FSB)

CPU Data StreamingWrite Streaming • Enable data streaming • But do not thrash private cache or shared cache • Write-through L1 caches • Uncached write gathering buffers in shared L2 for each core (for later dumping to FSB) • Cacheable write gathering buffers (for data transformation workloads)

CPU Data StreamingRead Streaming Custom prefetch instruction separates read streaming from write streaming L2 cache is not thrashed

Conclusion Picture taken from: http://www-128.ibm.com/developerworks/library/pa-fpfxbox/

Discussion The End Any Questions?

References • Application Customized CPU Design, http://www-128.ibm.com/developerworks/power/library/pa-fpfxbox/index.html, 2005. • J. Andrews, N. Baker, “Xbox 360 Architecture”, IEEE Macro, vol. 26, no. 2, pp. 25-37, 2006. • PowerPC – Wikipedia, the free encyclopedia, http://en.wikipedia.org/wiki/Powerpc, 2006. • Xbox 360 Architecture,www.hotchips.org/archives/hc17/3_Tue/HC17.S8/HC17.S8T4.pdf, 2006.