MonolithIC 3D ICs

MonolithIC 3D ICs. October 2012. MonolithIC 3D Inc. , Patents Pending. The Monolithic 3D Innovation. Utilize Ion-Cut (‘Smart-Cut’) to transfer a thin (<100nm) single crystal layer on top of the bottom (base) wafer Form the cut at less than 400ºC * Use co-implant

MonolithIC 3D ICs

E N D

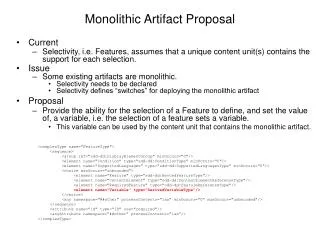

Presentation Transcript

MonolithIC 3D ICs October 2012 MonolithIC 3D Inc. , Patents Pending MonolithIC 3D Inc. , Patents Pending

The Monolithic 3D Innovation • Utilize Ion-Cut (‘Smart-Cut’) to transfer a thin (<100nm) single crystal layer on top of the bottom (base) wafer • Form the cut at less than 400ºC * • Use co-implant • Use mechanically assisted cleaving • Form the bonding at less than 400ºC * * See details at: Low Temperature Cleaving,Low Temperature Wafer Direct Bonding • Split the transistor processing to two portions • High temperature process portion (ion implant and activation) to be done before the Ion-Cut • Low temperature (<400°C) process portion (etch and deposition) to be done after layer transfer See details in the following slides:

Monolithic 3D ICs Using SmartCut technology - the ion cutting process that Soitec uses to make SOI wafers for AMD and IBM (millions of wafers had utilized the process over the last 20 years) - to stack up consecutive layers of active silicon (bond first and then cut). Soitec’s Smart Cut Patented* Flow: *Soitec’s fundamental patent US 5,374,564 expired Sep. 15, 2012 MonolithIC 3D Inc. , Patents Pending

Monolithic 3D ICs Ion cutting: the key idea is that if you implant a thin layer of H+ ions into a single crystal of silicon, the ions will weaken the bonds between the neighboring silicon atoms, creating a fracture plane (Figure 3). Judicious force will then precisely break the wafer at the plane of the H+ implant, allowing you to in-effect peel off very thin layer. This technique is currently being used to produce the most advanced transistors (Fully Depleted SOI, UTBB transistors – Ultra Thin Body and BOX), forming monocrystalline silicon layers that are less than 10nm thick. MonolithIC 3D Inc. , Patents Pending

Figure 3Using ion-cutting to place a thin layer of monocrystalline silicon above a processed (transistors and metallization) base wafer Cleave using <400oC anneal or sideways mechanical force. CMP. Hydrogen implant of top layer Flip top layer and bond to bottom layer Oxide p- Si Top layer Oxide p- Si H p- Si H p- Si Oxide Oxide Oxide Oxide Oxide Bottom layer Similar process (bulk-to-bulk) used for manufacturing all SOI wafers today MonolithIC 3D Inc. , Patents Pending

Chapter 3 Monolithic 3D HKMG MonolithIC 3D Inc. Patents Pending

Technology The monolithic 3D IC technology is applied to produce monolithically stacked high performance High-k Metal Gate (HKMG) devices, the world’s most advanced production transistors.3D Monolithic State-of-the-Art transistors are formed with ion-cut applied to a gate-last process, combined with a low temperature face-up layer transfer, repeating layouts, and an innovative inter-layer via (ILV) alignment scheme.Monolithic 3D IC provides a path to reduce logic, SOC, and memory costs without investing in expensive scaling down. MonolithIC 3D Inc. Patents Pending

On the donor wafer, fabricate standard dummy gates with oxide and poly-Si; >900ºC OK Poly Oxide NMOS PMOS ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Form transistor source/drain Poly Oxide NMOS PMOS ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Form inter layer dielectric (ILD), S/D implants and high temp anneals, CMP to transistor tops CMP to top of dummy gates S/D Implant ILD NMOS PMOS ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Implant hydrogen to generate cleave plane NMOS PMOS ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Implant hydrogen to generate cleave plane NMOS PMOS ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Implant hydrogen to generate cleave plane NMOS PMOS H+ ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Bond donor wafer to carrier wafer ~700µm Carrier Wafer H+ ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

Cleave to remove bulk of donor wafer ~700µm Carrier Wafer Transferred Donor Layer Silicon H+ ~700µm Donor Wafer Silicon MonolithIC 3D Inc. Patents Pending

CMP to STI ~700µm Carrier Wafer Transferred Donor Layer STI MonolithIC 3D Inc. Patents Pending

Deposit oxide, ox-ox bond carrier structure to base wafer that has transistors & circuits ~700µm Carrier Wafer Transferred Donor Layer STI Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending

Remove carrier wafer ~700µm Carrier Wafer Transferred Donor Layer Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending

Carrier wafer had been removed Transferred Donor Layer Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending 19

Replace dummy gate stacks with Hafnium Oxide & metal at low temp Note: Replacing oxide and gate result in oxide and gate that were not damaged by the H+ implant Transferred Donor Layer Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending

Form inter layer via through oxide only (similar to standard via) Note: The second mono-crystal layer is very thin (<100nm) and via through it, is similar to other vias in the metal stack Transferred Donor Layer Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending

Form top layer interconnect and connect layers with inter layer via ILV Transferred Donor Layer Oxide-oxide bond Base Wafer NMOS PMOS MonolithIC 3D Inc. Patents Pending MonolithIC 3D Inc. Patents Pending

Novel Alignment Scheme using Repeating Layouts Oxide Landing pad Through-layer connection Bottom layer layout Top layer layout 23 MonolithIC 3D Inc. Patents Pending Even if misalignment occurs during bonding repeating layouts allow correct connections. Above representation simplistic (high area penalty).

Smart Alignment Scheme Oxide Landing pad Through-layer connection Bottom layer layout Top layer layout 24 MonolithIC 3D Inc. Patents Pending