Virtual Memory Review

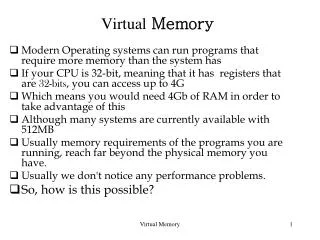

This review provides an overview of virtual memory and its strategies for giving the illusion of a large memory, allowing processes to share a single memory. It discusses address translation, page faults, TLB, optimizations, and memory organization.

Virtual Memory Review

E N D

Presentation Transcript

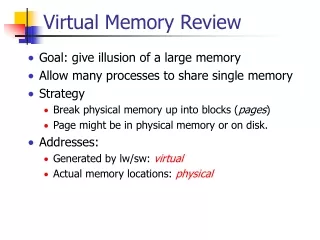

Virtual Memory Review • Goal: give illusion of a large memory • Allow many processes to share single memory • Strategy • Break physical memory up into blocks (pages) • Page might be in physical memory or on disk. • Addresses: • Generated by lw/sw: virtual • Actual memory locations: physical

Memory access • Load/store/PC computes a virtual address • Need address translation • Convert virtual addr to physical addr • Use page table for lookup • Check virtual address: • If page is in memory, access memory with physical address • May also need to check access permissions • If page is in not in memory, access disk • Page fault • Slow – so run another program while it’s doing that • Do translation in hardware • Software translation would be too slow!

Handling a page fault • Occurs during memory access clock cycle • Handler must: • Find disk address from page table entry • Choose physical page to replace • if page dirty, write to disk first • Read referenced page from disk into physical page

TLB: Translation Lookaside Buffer • Address translation has a high degree of locality • If page accessed once, highly likely to be accessed again soon. • So, cache a few frequently used page table entries • TLB = hardware cache for the page table • Make translation faster • Small, usually fully-associative • TLB entries contain • Valid bit = TLB hit • Other housekeeping bits • Tag = virtual page number • Data = Physical page number • Misses handled in hardware (dedicated FSM) or software (OS code reads page table)

TLB Misses • TLB miss means one of two things • Page is present in memory, need to create the missing mapping in the TLB • Page is not present in memory (page fault), need to transfer control to OS to deal with it. • Need to generate an exception • Copy page table entry to TLB – use appropriate replacement algorithm if you need to evict an entry from TLB.

Optimizations • Make the common case fast • Speed up TLB hit + L1 Cache hit • Do TLB lookup and cache lookup in parallel • Possible if cache index is independent of virtual address translation • Have cache indexed by virtual addresses

TLB Example - 7.32, 7.33 • Given: • 40-bit virtual addr • 16KB pages • 36-bit physical byte address • 2-way set associative TLB with 256 total entries • Total page table size? • Memory organization?

Page table/address parameters • 16KB=2^14, so 16K pages need 14 bits for an offset inside a page. • The rest of the virtual address is the virtual page index, and it's 40-14 = 26 bits long, for 2^26 page table entries. • Each entry contains 4 bits for valid/protection/dirty information, and the physical frame number, which is 36-14 = 22 bits long, for a total of 26 bits. • The total page table size is then 26 bits * 2^26 entries = 208 MB

Memory organization 26-bit virtual page number tag index page offset 19 7 14 valid/etc. Tag physical page # valid/etc. tag physical page # 0 1 2 3 = = … … … … 126 127 22 TLB: 128 sets, each w/2 entries 22 2-1 MUX Physical Address physical page # page offset 22 14

Fun stuff: bootstrapping on x86 • You power up your PC, what happens? • Hardware reset • Initialize all bits of cache, regs, buffers, etc. to a known value; go to real mode • EIP (PC) initialized to 0x0000FFF0, base address (CS) initialized to 0xFFFF0000 • So execution begins at 0xFFFFFFF0, 16 bytes from top of physical memory, in EPROM. • EPROM remapped to this high address by system chipset • First things to execute in EPROM • set up IDT = interrupt descriptor table • Jump to the BIOS

Bootstrapping 2 • BIOS: basic input/output system • Built-in software that determines what a computer can do without accessing programs from a disk • Placed in ROM chip that comes with the PC • BIOS and booting • BIOS will search devices in specified order for bootable ones • Take the current boot disk • Load first sector (usually 512 bytes) at 0000:7C00. • Look for a special signature (0xAA55) at the end of it (the last two bytes) • Signature not there: “Invalid / Non System Disk” error • If signature ok, start executing code in this sector • Code limited to 512 bytes! • Probably jump to secondary boot program, which will load OS

Bootstrapping 3 • For hard disks, first sector is the MBR = Master Boot Record • MBR has three parts • Code to load a bootsector from one of four primary partitions • Top level partition table for hard drive, at offset 446. Has four 16-byte records. • Magic values at offsets 510-511: 0xAA55 • Sector 0 of HD partition contains actual bootloader. • Either finds/loads OS, or loads secondary bootloader

Inside a bootloader • Get disk geometry for floppies • Find second-stage loader if need >512 bytes for code. • Load it • Get/check system info • Check for 32-bit CPU • Check for fast enough CPU • Detect drives and their geometries • Find/load config file • Present a boot menu to the user • Store magic values – which bootloader was used, drive we booted from, etc. • Find/validate/copy/load kernel • Floppy: when done loading, turn off floppy drive motor :) • mov dx,3F2h mov al,0 out dx,al