EECE 320: Digital Systems Design Lectures 34 Iterative/Sequential Arithmetic Circuits

270 likes | 290 Vues

EECE 320: Digital Systems Design Lectures 34 Iterative/Sequential Arithmetic Circuits. Ali Chehab. Multiplicand 1 0 0 0 ten Multiplier x 1 0 0 1 ten 1 0 0 0

EECE 320: Digital Systems Design Lectures 34 Iterative/Sequential Arithmetic Circuits

E N D

Presentation Transcript

EECE 320: Digital Systems DesignLectures 34Iterative/Sequential Arithmetic Circuits Ali Chehab

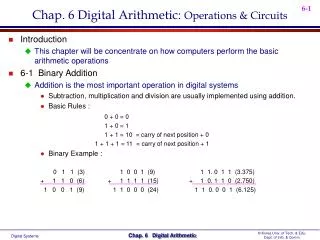

Multiplicand 1 0 0 0ten Multiplier x 1 0 0 1ten 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0ten Recap of Unsigned Multiplication • Paper and pencil unsigned multiplication example: • Multiplication in binary is easy: • 0 multiplier: place a 0 (0 x multiplicand) • 1 multiplier: place a copy of multiplicand (1 x multiplicand) • m bits xn bits --> m + n bit product. • Already considered unsigned combinational array multiplier. • Not practical for large m and/or n.

64-bit ADDER LSB Sequential Multiplier - I • Mimic paper and pencil multiplication algorithm. • Assume Multiplier and Multiplicand are 32 bits; Hence product is 64 bits long. • Assume a 64-bit Adder, a 32-bit Multiplier register initialized with multiplier, a 64-bit Product register initialized to 0, and a 64-bit Multiplicand register. • Initialize right half of Multiplicand register with the multiplicand, and 0 in the left half. • At each step, shift Multiplicand left by 1 as it may be added to partial products if multiplier bit is 1.

Example 1 • Using 4-bit numbers, multiply 0010 x 0011.

ADD SUB LSB Sequential Multiplier - II • Observations: • Half the bits in Multiplicand always 0 => 64-bit adder is wasteful and slow. • Effectively, addition is performed only with 32 bits, hence, Multiplicand can be stored in a 32-bit register instead of 64. • Multiplicand is shifted left with 0 fill-in, so Multiplicand cannot affect the LSBs of the Product: • P63P62…P4P3P2P1P0 + 000…0 Multiplicand 000 = P’63P’62…P’4P’3P2P1P0 • Instead of shifting Multiplicand to left, can we shift Product to right? • Now Multiplicand would be fixed relative to Product. • Work with 32-bit numbers, and hence adder need only be 32-bits wide!

Example 2 • Multiply 0010 x 0011 using version 2 of the multiplier.

ADD SUB LSB Sequential Multiplier - III • Observations: • Product register has wasted space that matches exactly the size of the Multiplier. • As the wasted space disappears, so do the bits of the Multiplier. • Hence we can combine the rightmost half of the Product with the Multiplier.

Example 3 • Multiply 0010 x 0011 using version 3 of the multiplier.

0 0 1 0ten x 0 1 1 0ten 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 1 1 0 0ten What about Signed Multiplication? • Basic approach: • Store the signs of the operands • Convert signed numbers to unsigned numbers (most significant bit (MSB) = 0) • Perform multiplication • If sign bits of operands are equal then sign of product bit = 0, else sign bit is 1. • Improved method: Booth's Algorithm • Assumption: Adder and Subtractor are available • Another motivation is to reduce the number of partial products by examining 2 or more bits of the multiplier. • Example: Multiply 2 x 6 = 0010 x 0110 • We can get the same result in another way: • For example, since 6 = -2 + 8 (0110 = -00010 + 01000, 0110 = 11110 + 01000) • We can replace a string of 1s in the multiplier with an initial subtract when we first see a 1, and then later add when we first see the bit after the last 1 in the string of 1s.

0 0 1 0ten x 0 1 1 0ten + 0 0 0 0 - 0 0 1 0 + 0 0 0 0 + 0 0 1 0 0 0 0 1 1 0 0ten Booth’s Algorithm • Algorithm: Scan the Multiplier from right to left and observe 2 bits at a time, the current bit and the previous bit. Depending on their value, do one of the following: • 00: Middle of a string of zeros, so no arithmetic operation. • 01: End of a string of 1s, so add the Multiplicand to the left half of the Product. • 10: Beginning of a string of 1s, so subtract Multiplicand from left half of the Product. • 11: Middle of a string of 1s, so no arithmetic operation. • Then shift the Product register right 1 bit.

Comparison Between Original and Booth’s Algorithms • Assumptions: • Assume previous bit at startup to be 0. • When shifting the Product, do sign extension (arithmetic shift operation) Arithmetic right shift: 1001010 --> 1100101 Logical right shift: 1001010 --> 0100101

Another Example • Try Booth’s algorithm with negative numbers: Multiply 2 by -3 = -6, or 0010 x 1101 = 1111 1010.

Why Does Booth’s Alg. Work for 2s Complement Numbers • Let a=an-1an-2…a0 be the Multiplier, and b be the Multiplicand. • Booth’s algorithm says that if • (ai-1 - ai) = 0, do nothing • (ai-1 - ai) = 1, add b • (ai-1 - ai) = -1, subtract b • Shifting the Multiplicand left with respect to the Product is equivalent to multiplying by a power of 2: • Sum can be simplified by noting that: • Recalling that a-1 = 0 and factoring out b, the sum reduces to:

0 1 0 1 1 1 0 1 1 0 0 1 0 -Mcand+2Mcand = Mcand 0 1 0 1 1 1 0 1 1 0 0 1 0 -2Mcand 0+2Mcand = 2Mcand 0 1 0 1 1 1 0 1 1 0 0 1 0 -Mcand + 0 0 1 0 1 1 1 0 1 1 0 0 1 0 0+2Mcand = 2Mcand 0 1 0 1 1 1 0 1 1 0 0 1 0 -Mcand+2Mcand = Mcand 0 1 0 1 1 1 0 1 1 0 0 1 0 Modified Booth’s: Can we examine more than 2 bits at a time? • What if we examine 3 bits of the multiplier at a time? • Requires only 6 steps to complete as opposed to 12 in original algorithm. • Can list all possible 8 values of the 3 bits considered and the action taken:

where Quotient 1 0 0 1 Divisor Dividend 1000 1001010 - 1000 0010 0101 1010 - 1000 Remainder 0010 Binary Division • Division is most complex of the four basic arithmetic operations. • Division of 2 operands, called Dividend (X) and Divisor (D), generates 2 results, Quotient (Q) and Remainder (R) that satisfy: • Example:

Binary Division • Basic division algorithm tries to see how big a number can be subtracted from Dividend, creating a bit of the quotient at each step. • For binary, it is easy to find out how many times the Divisor goes into the portion of the Dividend. • It is either 0 x Divisor, or 1 x Divisor. • In typical arithmetic units, where operands are represented using n-bits (single-length registers), a double length product (2n bits) is available after a multiply operation. • We wish to allow the use of this result in a subsequent Divide operation. • Hence Dividend (X) is represented using 2n bits, while D,Q, and R are represented using n bits. • To make sure that Q fits in n bits (i.e., Q<2n assuming unsigned numbers), • We must have X < 2n D, otherwise, we have an overflow condition. • EX: if Divisor=1, get an overflow if X >= 2n. • Also need to check that Divisor 0 • Generate a Divide-by-zero signal when D=0. • First we assume all numbers are unsigned, and perform division. • Later generalize for signed numbers: • sign(Quotient) = -1 iff sign(Dividend) sign(Divisor) • sign(Remainder) = sign(Dividend)

64-bit ADD/SUB Divider - I • Assume Dividend is a 64-bit number and Divisor a 32-bit number (such that X < 232 D). • Registers used to store operands and results: • 64-bit Divisor register with Divisor stored in left half (to allow for aligning divisor with Dividend), • 32-bit Quotient register • 64-bit Remainder register initialized with the Dividend • Divider uses a 64-bit adder/subtractor to perform division.

S t a r t 1 . S u b t r a c t t h e D i v i s o r r e g i s t e r f r o m t h e R e m a i n d e r r e g i s t e r a n d p l a c e t h e r e s u l t i n t h e R e m a i n d e r r e g i s t e r R e m a i n d e r 0 R e m a i n d e r < 0 T e s t R e m a i n d e r leave restore 2 a . S h i f t t h e Q u o t i e n t r e g i s t e r t o t h e l e f t , 2 b . R e s t o r e t h e o r i g i n a l v a l u e b y a d d i n g s e t t i n g t h e n e w r i g h t m o s t b i t t o 1 t h e D i v i s o r r e g i s t e r t o t h e R e m a i n d e r r e g i s t e r a n d p l a c e t h e s u m i n t h e R e m a i n d e r r e g i s t e r . A l s o s h i f t t h e Q u o t i e n t r e g i s t e r t o t h e l e f t , s e t t i n g t h e n e w l e a s t s i g n i f i c a n t b i t t o 0 3 . S h i f t t h e D i v i s o r r e g i s t e r r i g h t 1 b i t N o : < 3 3 r e p e t i t i o n s 3 3 r d r e p e t i t i o n ? Y e s : 3 3 r e p e t i t i o n s D o n e Divider - I • For n-bit Quotient and Remainder, algorithm requires n+1 steps to complete. • First step of algorithm cannot generate a Quotient bit of 1 because the condition X < 232 D must be satisfied. • Note that placing the divisor in the left half of the 64-bit Divisor register is equivalent to multiplying D by 232. • Since Remainder register is initialized with X (Dividend), then the first time we compare R to Divisor register we get • Hence result of first step is useless.

Example - Divider 1 • Divide 7 by 2: 0000 0111 : 0010 Shift left logical

ADD SUB Divider - II • Since at most half of Divisor register has useful info, both Divisor and Adder/Subtractor sizes can be cut in half. • Shifting the Remainder to the left instead of shifting Divisor to the right achieves the required alignment and simplifies the hardware. • Remainder is still initialized with Dividend. • The useless first step of the previous algorithm can be eliminated by switching the order of the operations to shift the Remainder register leftfirst and then subtract Divisor from left half of the Remainder register. • When the algorithm terminates, the remainder will be in the left half of the Remainder register.

32-bit ADD/SUB Divider - III • Similar to the third version of the multiplication algorithm, the Quotient register can be eliminated by shifting the bits of the quotient into the Remainder register instead of shifting 0s as in preceding algorithm. • Start by shifting the Remainder left as before • Therefore the loop contains only 2 steps because the shifting of the Remainder register shifts both the remainder in the left half and quotient in the right half. • The consequence of combining the 2 registers together and the new order of the operations in the loop is that the remainder will be shifted left one time too many to make room for the last quotient bit on the right. • Thus the final correction step must shift back only the remainder in the left half of the register.

S t a r t 1 . S h i f t t h e R e m a i n d e r r e g i s t e r l e f t 1 b i t 2 . S u b t r a c t t h e D i v i s o r r e g i s t e r f r o m t h e l e f t h a l f o f t h e R e m a i n d e r r e g i s t e r a n d p l a c e t h e r e s u l t i n t h e l e f t h a l f o f t h e R e m a i n d e r r e g i s t e r R e m a i n d e r 0 R e m a i n d e r < 0 T e s t R e m a i n d e r 3 a . S h i f t t h e R e m a i n d e r r e g i s t e r t o t h e 3 b . R e s t o r e t h e o r i g i n a l v a l u e b y a d d i n g l e f t , s e t t i n g t h e n e w r i g h t m o s t b i t t o 1 t h e D i v i s o r r e g i s t e r t o t h e l e f t h a l f o f t h e R e m a i n d e r r e g i s t e r a n d p l a c e t h e s u m i n t h e l e f t h a l f o f t h e R e m a i n d e r r e g i s t e r . A l s o s h i f t t h e R e m a i n d e r r e g i s t e r t o t h e l e f t , s e t t i n g t h e n e w r i g h t m o s t b i t t o 0 N o : < 3 2 r e p e t i t i o n s 3 2 n d r e p e t i t i o n ? Y e s : 3 2 r e p e t i t i o n s D o n e . S h i f t l e f t h a l f o f R e m a i n d e r r i g h t 1 b i t Divider - III • Requires same hardware as shift-and-add multiplier.

Example • Divide 7 by 2: 0000 0111 by 0010

Signed Division • Simplest way is to remember signs, make operands positive, divide, and at the end complementation of Quotient and Remainder may be necessary. • Set sign of Quotient to -1 if Sign(Dividend) Sign(Divisor) • Sign(Remainder) = Sign(Dividend) • Example: +7 ÷ -2: Quotient = -3, Remainder = +1 • -7 ÷ -2: Quotient = +3, Remainder = -1