Efficient Storage of Defect Maps for Nanoscale Memory

250 likes | 391 Vues

Efficient Storage of Defect Maps for Nanoscale Memory. Susmit Biswas Tzvetan S. Metodi* Frederic T. Chong Ryan Kastner Tim Sherwood {susmit,chong,sherwood}@cs.ucsb.edu, kastner@ece.ucsb.edu, tsmetodiev@ucdavis.edu. *. Nanotechnology in Action. Scaling limit of CMOS Vdd ~ 1V Leakage

Efficient Storage of Defect Maps for Nanoscale Memory

E N D

Presentation Transcript

Efficient Storage of Defect Maps for Nanoscale Memory Susmit Biswas Tzvetan S. Metodi* Frederic T. Chong Ryan Kastner Tim Sherwood {susmit,chong,sherwood}@cs.ucsb.edu, kastner@ece.ucsb.edu, tsmetodiev@ucdavis.edu *

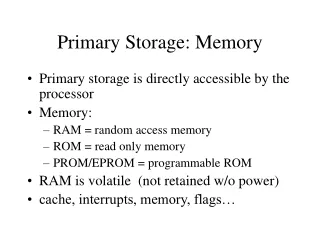

Nanotechnology in Action • Scaling limit of CMOS • Vdd ~ 1V • Leakage • Design of new nanoscale devices • SONOS, CMOL, Crossbar memories • CNT interconnect

Nanotechnology: Pros and Cons • Higher Density • 5nm<=Fnano <= 10nm • Faster operation • Fast switching • Low active power • Inexpensive • Reliability • Manufacturing defects might be as high as 10% [DeHon-NanoTech2005]

Solution: Reconfiguration • Dynamic • High latency in testing • Static: Defect Map • Using bit-level reconfiguration • High overhead in storage • Block level reconfiguration Efficient storage techniques !

Presentation overview • Motivation • Prior Work • Our Approach • Algorithms • Results • Conclusion

Prior Work • 1D list of regions [sun-NanoArch-06] • Bloom filter defect map [Wang-ICCAD2006]

Map of good regions • List based approach • Ranges • 1D • 2D • Can be stored in TCAM • Good for correlated defects

Equivalent Problem:Finding optimal rectangle cover • NP-Complete problem • Greedy Algorithm • R-Tree as data structure • New point inserted greedily for least increase in rectangle area • Suitable for storing ranges • k-means clustering to decide the insertion order of points

6 R4 3 1 R5 8 R2 R1 R6 7 5 2 R3 4 Algorithm 1: Illustration Root R1 R2 R5 R3 R6 R4

Storing Sparse Defect Locations • Bloom filter defect map [Wang-ICCAD2006] • Supports membership queries • Uniform hash function • No false negative • False positive • Better storage efficiency than bit vector D={d1, d2,…, dn} H1(d1) H2 (d1) H3 (d1) H4 (d1)

6 R4 3 1 R5 8 R2 R1 R6 7 5 2 R3 4 Algorithm 2: Illustration Root R1 R2 R3 R4

Experiments • Error Model • Gaussian distribution • Test data • Synthetic • TCAM: 128 Entry • Bloom filter: 5 times number of points

Conclusion • Defect map storage techniques • Region based • Combined approach with Bloom filter • Error model • Need of Finer model

Questions? Thanks!

References [sun-NanoArch-06] “Two Fault Tolerance Design Approaches for Hybrid CMOS / Nanodevice Digital Memories”,Fei Sun and Tong Zhang, NanoArch ’06 [Wang-ICCAD2006]“On The Use of Bloom Filters for Defect Maps in Nanocomputing”, Gang Wang, Wenrui Gong, Ryan Kastner, ICCAD ’06 [DeHon-NanoTech2005]“Non-Photolithographic Nanoscale Memory Density Prospects”, André DeHon, Seth Copen Goldstein, Philip J. Kuekes, and Patrick Lincoln, IEEE Tr. Nanotechnology ’05 [Nicolaidis-JET2005] “Memory Defect Tolerance Architectures for Nanotechnologies”,Michael Nicolaidis, Lorena Anghel, Nadir Achouri, Journal of El. Test. 2005