JTAG and Multi-ICE

180 likes | 325 Vues

This document outlines the ARM debugging architecture, emphasizing JTAG and Multi-ICE methodologies. It covers the fundamental aspects of ARM debug architecture, including the functionalities of the ARMulator and Multi-ICE hardware. Topics include serial scan path principles of JTAG, essential signals like TDI, TDO, and TCK, and the use of Multi-ICE for network debugging. Various requirements for ID checking algorithms are discussed, illustrating how to validate identifier formats while analyzing memory and cycle needs for effective debugging and performance profiling.

JTAG and Multi-ICE

E N D

Presentation Transcript

JTAG and Multi-ICE National Taiwan University Adopted from National Taiwan University SOC Course Material

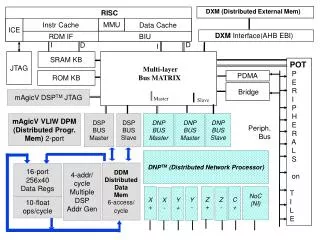

Outline • ARM debug Architecture • Content of JTAG • Multi-ICE Arch.

ARM debug Arch.(I) • AXD can debug design through: • – ARMulator (software) • – Multi-ICE (hardware) • – Angel (hardware)

ARM debug Arch.(II) • ARMulator • Processor core model • Handles all communication with the debugger • Memory interface • Transfers data between the ARM model and the memory model • Coprocessor interface • Can be used to simulate attached ARM-style coprocessors (such as floating point accelerators or custom DSPs) • Operating system interface • It is called whenever the ARM executes a SWI instruction, so you can simulate the operating system in C without having to write any ARM code.

ARM debug Arch.(III) • Multi-ICE • The solution for ARMulator limits • Can emulate custom logic • Use hardware to emulate truly results • Extended from JTAG Architecture

Outline • ARM debug Architecture • Content of JTAG • Multi-ICE Arch.

JTAG Arch. • Serial scan path from one cell to another

JTAG Principle(II) • JTAG Signals • TRST Test reset signal • TDI Test data in • TMS Test mode select • TCK Test clock • TDO Test data out

Outline • ARM debug Architecture • Content of JTAG • Multi-ICE Arch.

Multi-ICE(II) • Debugging software can be run on different computer through Network.

The portmap application • To support network connections, an additional application must be running on the windows workstation that runs the The multi-ICE server. • the portmapper allows software on other computers on the network to locate the multi-ICE server.

Multi-ICE [DUI_0048F_MICE2_2_UG] AXD and armsd Debuggers Guide [DUI_0066D_AXDDG_2_UG ] Getting Started Guide [DUI_0064D_GSG_UG ] Reference Topic & Related Documents

Experiment Requirements (1/3) • Write an ID checking engine and a front–end interface. • Requirements: • The front-end interface can accept up to 64 entries of ID in each round. • The program runs continuously round by round. • User input: • The amount of ID to be checked. • The ID numbers. • Program output: • The ID number. • Check result.

Experiment Requirements (2/3) • Example: (start of round) How many IDs to check: 2 Enter ID #1: A123456789 Enter ID #2: B987654321 === check result === A123456789 valid B987654321 invalid (end of round)

Experiment Requirements (3/3) • ID Checking Rules: • ID number comes in a 10-digit set. The ID starts with an alphabet, followed by 9 digits of numeral. • Checking the first numeral, it should be either “1” or “2”. • Setting some constrains to select valid IDs. • Recording the total memory and cycle requirements. • Constructing a profile to analysis the time percentage of each function in your code.