Alternative Gate Stack PMOS

Alternative Gate Stack PMOS. Presented by: Valarie Welsh Senior Research Proposal February 18, 2004. CMOS Issues with Poly-Si Gate. High Gate Resistance Premature Gate Depletion Boron Penetration Current Leakage. High Gate Resistance.

Alternative Gate Stack PMOS

E N D

Presentation Transcript

Alternative Gate Stack PMOS Presented by: Valarie Welsh Senior Research Proposal February 18, 2004

CMOS Issues with Poly-Si Gate • High Gate Resistance • Premature Gate Depletion • Boron Penetration • Current Leakage

High Gate Resistance • Resistances should be minimized for switching speeds • Alternative gate materials, specifically conductors are attractive for this purpose

Gate Depletion • Dopant from poly can diffuse into and through thin

Boron Penetration • Ultimate in dopant migration can affect channel length.

Current Leakage P-type regions beneath very thin gate with n+ doped poly are susceptible to tunneling effects opposite of the gate depletion and boron penetration mechanism

Gate Stack Engineering • Refers to finding new gate and new dielectrics materials • Work on alternative gate material • Material should: • Be compatible with gate dielectric • Have appropriate work function • Fit into to existing manufacture processes

Alternative Gate Material • Molybdenum – transition metal • Tg=2617°C • Stable contact with SiO2 to 1000°C • WK Fcn 4.7 Variable with process

Potential Solution to: • High Gate Resistance • Premature Gate Depletion • Boron Penetration • Current Leakage

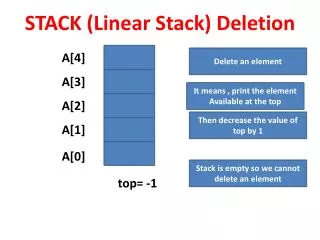

- - - - - - - - - - - - - - - - Process Plan A

Potential Problems • Finding previous work on self aligned gate process using Mo. Is there a reason why? • Looking for Mo application specs (sputter or other) usable in RIT’s fab • Source/Drain implants must be recalculated to compensate for gate treatment

Process Plan B • Same 5 Lith levels but no self aligning gate • Apply Mo outside RIT FAB

To Do: • Locate Mo application and etch process for use at RIT • Simulation to establish whether workfunction adjustment is warranted • Final establishment of process • Certifications

References: • P. Ranade, “Molybdenum as a gate electrode for deep sub-micron CMOS technology”, Mat. Res. Soc. Symp. Vol. 611,2000, p.C3.2.1 • K. Han, “Gate Stack Engineering: Advanced Process Integration for VLSI”, Research Paper. Fall 2001 • C.H. Choi et.al., “Direct Tunneling Current Model for Circuit Simulation”, Center for Integrated Systems, Stanford University, Stanford, CA • R.P.S. Thakur, Y.Chen, E.H.Poindexter, and R.Singh, “Silicon-Based Ultrathin Dielectrics”, The Electrochemical Society Interface, Summer 1999