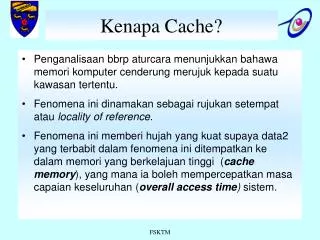

Kenapa Cache?

Kenapa Cache?. Penganalisaan bbrp aturcara menunjukkan bahawa memori komputer cenderung merujuk kepada suatu kawasan tertentu. Fenomena ini dinamakan sebagai rujukan setempat atau locality of reference .

Kenapa Cache?

E N D

Presentation Transcript

Kenapa Cache? • Penganalisaan bbrp aturcara menunjukkan bahawa memori komputer cenderung merujuk kepada suatu kawasan tertentu. • Fenomena ini dinamakan sebagai rujukan setempat atau locality of reference. • Fenomena ini memberi hujah yang kuat supaya data2 yang terbabit dalam fenomena ini ditempatkan ke dalam memori yang berkelajuan tinggi (cache memory), yang mana ia boleh mempercepatkan masa capaian keseluruhan (overall access time) sistem.

Data Bus Komputer Dgn Cache Processor Main Memory Cache Memory Address Bus

Sebilangan kecil memori berkelajuan tinggi. Ia berada di antara memori utama dan pemproses (CPU) Berkemungkinan juga terletak dalam cip CPU atau modul. Cache

CPU memohon kandungan bg lokasi memori yang diperlukan. Semak data ini di cache Jika ada, ambil drpd cache (cepat) Jika tiada, baca blok yg diperlukan drps memori utama ke cache Kemudian, hantarnya drpd cache ke CPU Cache ada tags utk mengenalpasti blok memori utama yang mana berada dalam setiap slot cache. Operasi Cache - Tinjauan

Saiz Fungsi Pemetaan (Mapping function) Aloritma Penggantian (Replacement algorithm) Polisi Baca (Write policy) Saiz Blok (Block size) Bilangan cache (Number of caches) Rekabentuk Cache

Kos (Cost) Lbh cache - mahal Kelajuan (Speed) Lbh cache – lbh laju (up to a point) Semakan cache – ambil lbh masa Saiz

Memori Cache • Cache: tempat selamat utk menyorok atau menyimpan data • Hierarki memori diantara CPU dan main memory • Mengurang masa capaian ke main memory • Kerap juga digunakan dalam peranti input/output • Cache menggunakan SRAM: Static Random Access Memory • No refresh

Cache Addressing START No Is Block inCache? Access main memoryfor block containing RA Yes Fetch RA word anddeliver to CPU Alloc. cache slot formain memory block Deliver RA word to CPU Load main memoryblock into cache slot DONE

Hit (Kena) Keadaan di mana pabila secebis data ingin dicapai drpd memori, data tersebut dijumpai berada di cache. Miss (Sipi) Keadaan di mana pabila secebis data ingin dicapai drpd memori, data tersebut tidak dijumpai di cache. Terminologi Cache

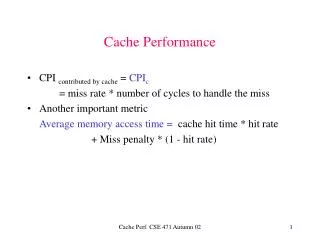

Hit ratio.(Nisbah kena) Nisbah (dlm %) bilangan capaian data yang berjaya dijumpai di. Keberkesanan cache blh diukur dengan hitungan hit ratio dan miss ratio, yakni, Prestasi Cache hit = 1 - miss

Take the following access time of A computer system, (Tma = 500ns) Based on the above, the overall access time to the memory with no cache is, Tacc = Tma = 500ns If the above system has a cache with an access time of 50ns (Tca) and a hit ratio of 90%, the overall access time is, Tacc = (Tca X 0.90) + (Tma X (1-0.9)) Tacc = (50 X 0.90) + (500 x 0.10) Tacc = (45) + (50) Tacc = 95ns Blhkah Cache Meningkatkan Prestasi Sistem?

Implementing a cache requires due consideration and tradeoffs between the following:- The Hit Ratio Access Time on a Hit Delay Time on a Miss Cost Pertimbangan Rekabentuk Cache

O/k cache senantiasa smaller drpd main memory, maka semestinya wujud cara bgmn main memory blh dipetakan ke cache yg kecil ini. Terdpt tiga keadah yg biasa digunakan:- Direct mapping Full associative mapping Set associative mapping Main Memory Cache Mapping Jenis2 Pemetaan Cache

Secara asasnya utk mencapai memori komputer ialah melalui addressbus. Oleh itu, lebar address bus menentukan bilangan memori yang boleh dicapai. Cth:-. Jika lebar addressbus ialah 15 bit, maka bilangan lokasi yg blh dialamatkan ialah:-. N = 15. 2n = lokasi. 215= 32768. Pemetaan Cache

Example of how the main memory is partitioned based on the address bus width. 0 . . . MEMORY . . CPU 32767 Pemetaan Cache

Utk m’benar’n main memory dipetakan ke cache, medan alamat dibhgkan kpd dua bhgn iaitu medan tag & medan index. 15 bits TAG INDEX 15 bits TAG INDEX 9 bits 6 bits Cache : Pemetaan Terus • Jika sistem ada 2n words dlm main memory dan 2k words dlm cache. • n = 15 • k = 9 • Tag Field Size = n - k • = 6

Example 0 0 Main Memory 32K X 12 Address = 15 bits Data = 12 bits Cache 512 X 12 Address = 9 bits Data = 12 bits 511 32767 Cache : Pemetaan Terus

Main memory 0 0 6 Bits 12 Bits 511 511 Data is stored here Tag Field 0 511 0 511 Cache : Pemetaan Terus Cache Tag 0 Tag 1 . . . . Tag 64 12 Bits

Memory Address Location Full Associative Mapping Main Memory Cache 12 291 291 12 65 803 803 65 15 Bits 12 Bits Full address is stored here Data is stored here 12 Bits

Address (Tag & Index) Decimal Form Binary Form 291 000000100100011 Tag Field Index Field 000001100100011 803 Tag Field Index Field

Set Associative Mapping Main Memory Cache 12 0 12 1 65 291 65 803 2-Way Set Associative Cache Tag Value is stored here Data is stored here 2-Way Set Associative Cache

Compulsory—capaian pertama ke blok tiada dlm cache, maka blok trersebut mesti dibawa kedlm cache. Ia juga dikenali sbg first reference misses. Capacity—jk cache t/blh mengisi kesemua blok yg diperlukan ketika perlaksanaan aturcara, capacity missesakan wujud disbbkan oleh blok terpaksa dibuang.(Misses in fully associative). Conflict—jk strategi penggantian adlh pemetaan set associative atau direct, conflict misses akan wujud krn blok tlh dibuang dan wujud capaian semula jk terlampau byk blok dipetakan kpd set. Juga dikenali sbg interference misses.(Misses in n-way associative). Classifying Misses

Apbila cache penuh, ia perlu menyediakan utk new entry dgn displacing an older entry dlm cache. Ini dinamakan replacementpolicy. Ada tiga kaedah:-. Least recently used. First in first out. Random. Polisi Penggantian Cache

Write-through. Data yg ditulis kpd cache, ia juga ditempatkan (ditulis) kedlm main memory ketika update. Write-back. Data yg ditulis kpd cache, ia tidak ditulis kedlm main memory. Main Memory Update Policy

Cth, jk data "12" ditulis ke primary storage, salinannya ditulis kedlm cache begitu juga main memory. Write Through Cache MAIN MEMORY 12 CACHE 12 CPU 12 Area Of Activity

Cth, jk data "12" ditulis ke primary storage, salinannya hanya ditulis kedlm cache. Main memory tidak diupdate. MAIN MEMORY CACHE CPU Write Back Cache 12 12 Area Of Activity