Computer Organization

Computer Organization. 講師:陳育良. 第一章. 計算機類型. 計算機類型. 個人電腦 桌上型 筆記型 工作站 企業級系統 伺服器 (low end): 資料庫 、 Web Server 大型主機 : 商業資料處理 超級電腦 (high end): 氣象、模擬、彈道. 計算機功能單元. I/O Input Output Memory CPU ALU Control Unit. 計算機處理的資訊. Instruction(machine instructions, c.f.statements) Program

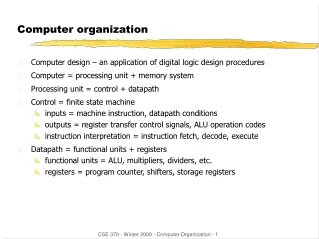

Computer Organization

E N D

Presentation Transcript

Computer Organization 講師:陳育良

第一章 • 計算機類型

計算機類型 • 個人電腦 • 桌上型 • 筆記型 • 工作站 • 企業級系統 • 伺服器(low end):資料庫、Web Server • 大型主機:商業資料處理 • 超級電腦(high end):氣象、模擬、彈道

計算機功能單元 • I/O • Input • Output • Memory • CPU • ALU • Control Unit

計算機處理的資訊 • Instruction(machine instructions, c.f.statements) • Program • Serial of instructions • Source program compiler Object Linkage Editor (reference to library) Image (executable) Loader Execution

資料編碼 • Bit -> byte -> word • BCD(binary-coded decimal) • Mainframe • ASCII(American Standard Code for Information Interchage) • 7 bits • EBCDIC(Extended Binary-Coded Decimal Interchange Code) • 8 bits

ASCII Table vs. EBCDIC Table • ASCII Table vs EBCDIC Table

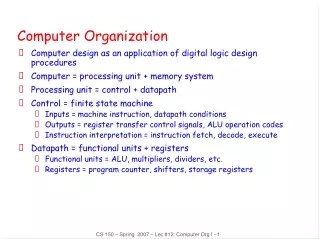

Functional Units • Input • Keyboard, mouse, joystick • Memory • Primary memory (DRAM、SDRAM-Synchronous DRAM ) • Address (byte) • Cache(SRAM-static random access memory ) • Secondary memory • Disk、Tape、CD-ROM

CPU • ALU(arithmetic and logic unit) • Registers (flip-flop)> Cache • high-speed storage area within the CPU • CU (control unit) • Instruction Decoder and control logic • Coordinator of other functional units • Sending control signals • Timng signal

Instruction example • Add Loca, R0 • Prefer • Load Local, R1 • Add R1, R0

Registers • IR (Instruction register) • PC (program counter) • General-purpose register • AX, BX, DX, CX(8086) • EAX,EBX,EDX,ECX(80x86) • MAR(memory address register) • Is the register of a computer's control unit that contains the address of a register to fetch or store from or to the computer storage. • The memory address register is half of a minimal interface between a microprogram and computer storage. The other half is a memory data register. • MDR(memory data register) • Is the register of a computer's control unit that contains the contents of a register to fetch or store from or to the computer storage. • The memory data register is half of a minimal interface between a microprogram and computer storage. The other half is a memory address register

Load Instruction(load Loca, R1) MAR <- PC; PC <- PC + 4; MDR <- MEM[MAR]; IR <- MDR; MAR <- Ra + ADJ6(IR[5:0]);(compute operand’s effective address) MDR <- MEM[MAR];(get operand) Rdest <- MDR;(write register)

Store Instruction(store Local, R1) MAR <- PC; PC <- PC + 4; MDR <- MEM[MAR]; IR <- MDR; MAR <- Ra + ADJ6(IR[5:0]); (compute operand’s effective address) MDR <- Rdest; (write MDR) MEM[MAR] <- MDR; (write memory)

Basic Computer Organization Revisited I/O Memory Data Processor Program General- Purpose Registers ALUs MAR MDR PC Control Logic

Interrupt • Preempt vs non-preempt • Hardware interrupt • I/O interrupt • Softwre interrupt • System calls • Interrupt-service routine • Context Switching • Keep status of CPU in stack

BUS • Connect various devices • Addressing lines • Control lines • Single bus • Low cost • Two devices talk at any time • Multiple bus • High cost • Allow concurrency, high efficiency

Buffer register • Equipped in devices for compensating the speed differences • Multiprogramming • CPU switches between running programs when they are blocked in I/O

System softwre I • Coordinate the activities within computer system • Compiler • High level language • Do not need to know the underlay CPU • Assembler • Assembly language • Need to know the architecture of CPU • Text editor

System softwre II • OS (Operating System) • Distribute and manage resources for application programs • Monolithic • Eg. Linux (but has been improved with loadable modules facility, also called kernel extension ) • Microkernel • Eg. Windows NT

OS characteristics • Multiprogramming • Multi-user vs. single user • Multitasking vs. single task • Time sharing • Preempted • Windows NT, Linux • Non-preempted • Windows 3.1

Performance • Hardware • cpu, memory hierarchy, pipelining, • dynamic scheduling (fetch-issue out of order), • Speculation (fetch-issue-execute) • Instruction set (CISC, RISC) • Compiler (optimization, instructions unrolling) • Processor time • Program + OS primitives

Memory hierarchy • Cache principle • L1 cache also called primary cache built into the CPU • L2 cache also called secondary cache, usually resides on a separate chip from CPU • Program characteristic • Temporal locality • Spatial locality

clock • Clock cycle (R) • Period (P) • R=1/P • Hz(Hertz) • Cycles per second(每秒震動的次數) • 500 MHz = 2 ns clock • 1.25 GHz = 0.8 ns clock

Basic performance equation • T = (N x S) / R • T: program execution time • N: Total number of Ins been executed (not equal to ins of object code for looping or no visiting) • S: Instruction stages • R: Clock rate • T -> down implies N,S down or R up • Due to the variety of S, 900MHz maybe run slow than 700MHz

Pipeline and superscalar • Pipeline • Overlapping the execution of instructions • Eg. Multiple workers in an assembly line of factory • Superscalar • Issue and execute multiple instructions at the same time with mutilple pipelines • Concurrent execution (must be the same with the results of sequential execution) • Eg. Multiple assembly lines

Instruction Set • CISC • Complex Instruction Set Computer • Eg. Intel CPU • RISC • Reduced Instruction Set Computer • Sun SPARC, Power PC, Alpha

Benchmark program • A baseline program for performance evaluation • Real applications of various domains selected from SPEC • SPEC (Standard Performance Evaluation Corporation) • SPEC95 – reference machine is SUN SPARC station 10/40 • SPEC2000 -300MHz UltraSPARC-Iii SUN SPARC 10 • SPEC evaluation= exe time of reference/exe time of target

Multiprocessor • Shared-memory multiprocessor • Multiple CPU share common memory • Message-passing multicomputer • Distributed computer architecuture • Every processor has local memory and communicates with each other via LAN

History(Stored program computer)by John Von Neumann • First generation – 1945~1955 • Vacuum tube • millisecond • Second generation – 1955~1965 • Transistor • microsecond • Third generation – 1965-1975 • IC • Microprogramming, pipeline, parallel, cache, virtual memory • Fourth generation – 1975 ~ • VLSI (very large scale integration) • Nanosecond