Report from 5th PXD DAQ Workshop Tokyo University, November 19-20, 2012

Tokyo Daigakku = „Todai“ symbol is Ginkgo leafs. Report from 5th PXD DAQ Workshop Tokyo University, November 19-20, 2012. http://kds.kek.jp/conferenceDisplay.py?confId=11242. organized by Higuchi-san (thanks!) 5th PXD DAQ Workshop was a VXD DAQ Workshop

Report from 5th PXD DAQ Workshop Tokyo University, November 19-20, 2012

E N D

Presentation Transcript

Tokyo Daigakku = „Todai“ symbol is Ginkgo leafs Report from 5th PXD DAQ WorkshopTokyo University, November 19-20, 2012

organized by Higuchi-san (thanks!) • 5th PXD DAQ Workshop was a VXD DAQ Workshop • dedicated almost 100% to DESY telescope test • Situation „as usual“ on PXD DAQ Workshop:presentations are interrupted frequently immediate discussion is fast, intelligent, direct, but always fair ! following what‘s going on by EVO difficult (maybe impossible) • DESY Test has 2 guidelines- Keep it as close to the final design - Keep it simple (whereever possible)

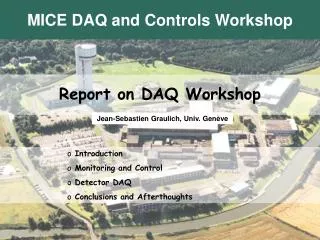

DATCON DESY Test Setup beam (silicon PM) FTSW 2 optical links 6 Gbps Trigger IN ROIs #1 (RJ45) KONTRON Switch DHH #1 RJ45 DHHC LVDS >>> JTAG <<< DHH #2 ATCA backplaneROI broadcast RJ45 ROIs #2 (RJ45) GbEto MicroBlaze PEDESTAL UPLOAD UDP(RJ45) PXD DATA FastRECO(basf2, root histos) Beam EVB #2 (SVD + PXD) EVB #1 (SVD only) SVD DATA HLT Junction Box Junction Box Copper FADC Control onlinetrack finderin basf2 FADC FADC VME Buffer Belle2Link FTB FTB updated versionpost-BGM 2 optical links2 Gbps

DESY Test – keep it close to the final design • We will use FTSW for timing/trigger distribution(as no beam clock, Nakao-san will generate clock) • There will be a DHHC • DHH will be new ATCA module, if readyfallback solution: existing 3 DHH VME modules • DCE3 will be used (this implies: data in cluster binary format) • LVDS cable length 15 m (over wall)with preemphasis • COPPER • new: PrPMC boards (PC daughter cards on COPPER, which receive digitized data from FINESSE) • new: multiple-event-DMA • Go up with the rate <10 kHz • ATCA-EVB: UDP with handshaking (not TCP/IP) • CO2 cooling (MARCO) and air cooling (T=−30o C) (dry air or nitrogen not decided yet)

DESY Test - Keep it „simple“ • PXD6 devices, not PXD9 (from Batch 3, possibly “mixed” designs)but a lot of development still to do(Cu metallization, flip chipping, kapton flex, testing etc.) • SVD modules: no wedges3 large sensors existing (from „drawers“ in Vienna)Markus´ idea: 4th module will be very first (4‘‘) Origami module (77.7 x 25.6 mm2) • DHH ! ONSEN: only 1 optical link! no Aurora channel bonding! no event building on ONSEN required • EVB: only 1 node (only 1 IP adress, point-to-point w/o packet loss)but parallellization in b2Socketsdata will be stored on USB disk

Goal of the Test as well: not only get data, but (a) filter data online and (b) try slow control scheme • ROI • HLT will be ¸ 5 PCs • will be reduced ! 48 bit already for DESY test • New result on ROI size by Pit Vonhoefer, pT=50-100 MeV/c! 40 x 40 pixels (large!) • quadratic ROIs are an option (advantage ! 32 bit)(reduction factor will be checked again with background data) • ROIs from 2 sources (HLT, DATCON) and ATCA backplane broadcast • outgoing data must be in sequence of HLT (need a protection, HLT must be 2nd to DATCON) • Slow control • There will be an „EPICS master“ (CSS+Archiver+Alarm Handler)! this simplifies the NSM-EPICS interface(i.e. the EPICS master is one NSM client) • IPbus for DHH (UDP stack for FPGA, no PowerPC, no Linux) • NSMv2 (64 bit) is baseline (NSMv1 is backup)

SVD readout(belle2link !) • requires two b2l cores on Spartan-6 • DATCON needs FTSW connection for flow control (not foreseen yet) • SVD event format (FADC format)still to be defined (Markus) • PXD data must be root-formattedfor PXD+SVD event building (requires basf2 module on EVB #2) K. Hara-san Higuchi-sanItoh-san Nakao-san

Logistics PCs (HLT, EVB, Slow Control)will be contributed by DESY(thank you very much) needs basf2

Compute Node v3 requires another iteration of Carrier Board (but not critical for DESY Test)

Next steps • More homework in Higuchi-san’s detailed summaryhttp://kds.kek.jp/getFile.py/access?contribId=28&sessionId=10&resId=0&materialId=slides&confId=11242 • Magnetic field in the cave (no flux return) is an overall concernshielding etc. must be foreseen • Combined DHP+DHH+ONSEN TestTUM+Giessen, around Wetzlar meeting @ Giessen • Next workshop Apr. 11th and 12th, 2013 @ DESY(incl. “gemba” meetings in the experimental hall) Thank you!

Beyond the DESY Test: issues for the PXD DAQ future • in the new accelerator scenario (A),there is no combined cosmic DAQ test anymore(PXD+SVD+other subdetectors) • Backpressure (flow control) not implementednot in belle2link, not in PXD DAQif buffers are full, data will be dropped! we need to think(option is ATCA rear transition module with LVDS to FTSW) • implications of revised neurotrigger (z trigger) design ?FPGA boards + Hough transform + multilayer preceptronwe decided that PXD DAQ (DATCON) does not need it as seed(because efficiency too low for these tracks) • new cabling schemeONSEN + DATCON will be located in E-Hut(if E-Hut is only radiation controlled area and can be accessed any time without stopping beam)