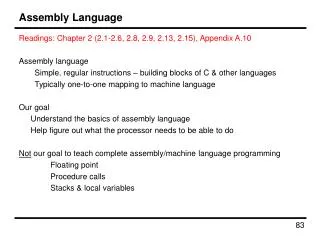

Assembly Language

Assembly Language. Basic Concepts IA-32 Processor Architecture. Hardware. Intel386, Intel486, Pentium, or latest processors, AMD processors, or compatible processors. The same architectures , but different organizations . Not working in MAC computers, SUN Sparc workstations.

Assembly Language

E N D

Presentation Transcript

Assembly Language Basic Concepts IA-32 Processor Architecture

Hardware • Intel386, Intel486, Pentium, or latest processors, AMD processors, or compatible processors. The same architectures, but different organizations. • Not working in MAC computers, SUN Sparc workstations.

Operating Systems • MS-DOS, Windows 95/98/ME/NT/2000/XP. • Advanced programs relating to direct hardware access and disk sector programming must be run under MS-DOS, Windows 95/98/ME. • Not working in Linux, MAC OS.

Programming Software • Editor: Microsoft Visual C++ (6.0, 2005 Express, 2008 Express), TextPad, Notepad. • Assembler and linker: MASM 6.15, MASM 8.0. • 32-but debugger: Microsoft Visual C++. • Other: MASM 32.

Two Types of Programs • 16-bit real-address mode: Run under MS-DOS and in the console window under MS-Windows. Written for the Intel 8086 and 8088 processors. Not discussed in this class. • 32-bit protected mode: All the programs in this class.

Build Environments • Get started: http://kipirvine.com/asm/gettingStarted/index.htm • Microsoft Visual C++ (6.0, 2005 Express, 2008 Express) installed. • Install MASM 8.0 (if 2005 Express is installed)

Build Environments • If Microsoft Visual C++ 6.0 is installed: • Install MASM 6.15 • Set tools: Build, run, and debug. http://kipirvine.com/asm/4th/ide/vs6/index.htm

A Simple C File • #include <stdio.h> • void main() • { • int i; • i = 0x10000; • i = i + 0x40000; • i = i - 0x20000; • printf("i= %d\n", i); • }

Into Assembly Language • 3: void main() • 4: { • 0040B450 push ebp • 0040B451 mov ebp,esp • 0040B453 sub esp,44h • 0040B456 push ebx • 0040B457 push esi • 0040B458 push edi • 0040B459 lea edi,[ebp-44h] • 0040B45C mov ecx,11h • 0040B461 mov eax,0CCCCCCCCh • 0040B466 rep stos dword ptr [edi] • 5: int i; • 6: • 7: i = 0x10000; • 0040B468 mov dword ptr [ebp-4],10000h

8: i = i + 0x40000; • 0040B46F mov eax,dword ptr [ebp-4] • 0040B472 add eax,40000h • 0040B477 mov dword ptr [ebp-4],eax • 9: i = i - 0x20000; • 0040B47A mov ecx,dword ptr [ebp-4] • 0040B47D sub ecx,20000h • 0040B483 mov dword ptr [ebp-4],ecx • 10: printf("i= %d\n", i); • 0040B486 mov edx,dword ptr [ebp-4] • 0040B489 push edx • 0040B48A push offset string "i= %d\n" (0041fe50) • 0040B48F call printf (0040b710) • 0040B494 add esp,8 • 11: }

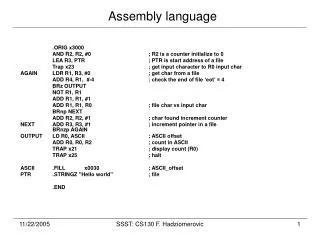

A Simple MASM File • TITLE Add and Subtract (AddSub.asm) • ; This program adds and subtracts 32-bit integers. • ; Last update: 2/1/02 • INCLUDE Irvine32.inc • .code • main PROC • mov eax,10000h ; EAX = 10000h • add eax,40000h ; EAX = 50000h • sub eax,20000h ; EAX = 30000h • call DumpRegs • exit • main ENDP • END main

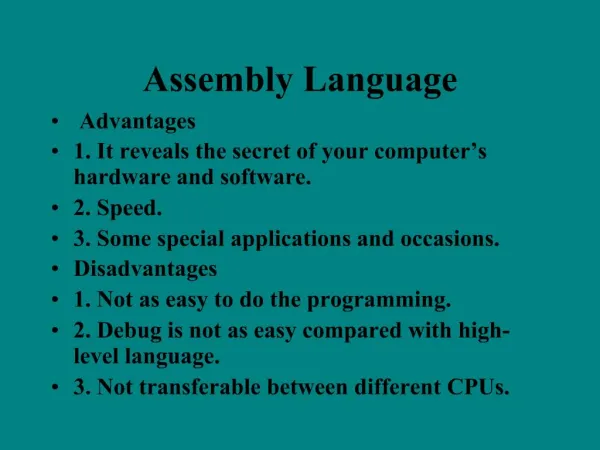

Portability • Assembly language is not portable. • Well-known processor families are Motorola 68x00, Intel IA-32, SUN Sparc, DEC Vax, and IBM-370.

Applications • Small embedded programs. • Real-time applications. • Computer game consoles. • Help understand computer hardware and operating systems. • Subroutines hand optimized for speed, for example, bitwise manipulation and data encryption. • Device drivers.

Applications • Small embedded programs. • Real-time applications. • Computer game consoles. • Help understand computer hardware and operating systems. • Subroutines hand optimized for speed, for example, bitwise manipulation and data encryption. • Device drivers.

Virtual Machines • Tanenbaum: Virtual machine concept • Programming Language analogy: • Each computer has a native machine language (language L0) that runs directly on its hardware • A more human-friendly language is usually constructed above machine language, called Language L1 • Programs written in L1 can run two different ways: • Interpretation – L0 program interprets and executes L1 instructions one by one • Translation – L1 program is completely translated into an L0 program, which then runs on the computer hardware Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Translating Languages English: Display the sum of A times B plus C. C++: cout << (A * B + C); Assembly Language: mov eax,A mul B add eax,C call WriteInt Intel Machine Language: A1 00000000 F7 25 00000004 03 05 00000008 E8 00500000 Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Specific Machine Levels (descriptions of individual levels follow . . . ) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

High-Level Language • Level 5 • Application-oriented languages • C++, Java, Pascal, Visual Basic . . . • Programs compile into assembly language (Level 4) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

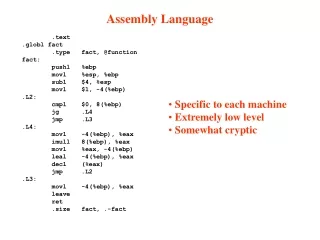

Assembly Language • Level 4 • Instruction mnemonics that have a one-to-one correspondence to machine language • Calls functions written at the operating system level (Level 3) • Programs are translated into machine language (Level 2) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Operating System • Level 3 • Provides services to Level 4 programs • Translated and run at the instruction set architecture level (Level 2) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Instruction Set Architecture • Level 2 • Also known as conventional machine language • Executed by Level 1 (microarchitecture) program Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Microarchitecture • Level 1 • Interprets conventional machine instructions (Level 2) • Executed by digital hardware (Level 0) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Digital Logic • Level 0 • CPU, constructed from digital logic gates • System bus • Memory • Implemented using bipolar transistors next: Data Representation Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Character Storage • Character sets • Standard ASCII (0 – 127) • Extended ASCII (0 – 255) • ANSI (0 – 255) • Unicode (0 – 65,535) • Null-terminated String • Array of characters followed by a null byte • Using the ASCII table • back inside cover of book Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Unicode Standard • UTF-8 • Used in HTML. • The same byte values as ASCII • UTF-16 • Windows NT, 2000, and XP. • UTF-32

Basic Microcomputer Design • clock synchronizes CPU operations • control unit (CU) coordinates sequence of execution steps • ALU performs arithmetic and bitwise processing Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Clock • synchronizes all CPU and BUS operations • machine (clock) cycle measures time of a single operation • clock is used to trigger events Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Instruction Execution Cycle • Fetch • Decode • Fetch operands • Execute • Store output Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Multi-Stage Pipeline • Pipelining makes it possible for processor to execute instructions in parallel • Instruction execution divided into discrete stages Example of a non-pipelined processor. Many wasted cycles. Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Pipelined Execution • More efficient use of cycles, greater throughput of instructions: For k states and n instructions, the number of required cycles is: k + (n – 1) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Wasted Cycles (pipelined) • When one of the stages requires two or more clock cycles, clock cycles are again wasted. For k states and n instructions, the number of required cycles is: k + (2n – 1) Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Superscalar A superscalar processor has multiple execution pipelines. In the following, note that Stage S4 has left and right pipelines (u and v). For k states and n instructions, the number of required cycles is: k + n Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Reading from Memory • Multiple machine cycles are required when reading from memory, because it responds much more slowly than the CPU. The steps are: • address placed on address bus • Read Line (RD) set low • CPU waits one cycle for memory to respond • Read Line (RD) goes to 1, indicating that the data is on the data bus Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Cache Memory • High-speed expensive static RAM both inside and outside the CPU. • Level-1 cache: inside the CPU • Level-2 cache: outside the CPU • Cache hit: when data to be read is already in cache memory • Cache miss: when data to be read is not in cache memory. Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

How a Program Runs Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Multitasking • OS can run multiple programs at the same time. • Multiple threads of execution within the same program. • Scheduler utility assigns a given amount of CPU time to each running program. • Rapid switching of tasks • gives illusion that all programs are running at once • the processor must support task switching. Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

IA-32 Processor Architecture • Modes of operation • Address space • Program registers • System registers • Floating-point unit • History

Modes of Operation • Protected mode • native mode (Windows, Linux) • Real-address mode • native MS-DOS • System management mode • power management, system security, diagnostics • Virtual-8086 mode • hybrid of Protected • each program has its own 8086 computer Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Basic Execution Environment • Addressable memory • General-purpose registers • Index and base registers • Specialized register uses • Status flags • Floating-point, MMX, XMM registers Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Addressable Memory • Protected mode • 4 GB • 32-bit address • Real-address and Virtual-8086 modes • 1 MB space • 20-bit address Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

General-Purpose Registers Named storage locations inside the CPU, optimized for speed. Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Accessing Parts of Registers • Use 8-bit name, 16-bit name, or 32-bit name • Applies to EAX, EBX, ECX, and EDX Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Index and Base Registers • Some registers have only a 16-bit name for their lower half: Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Some Specialized Register Uses (1 of 2) • General-Purpose • EAX – accumulator • ECX – loop counter • ESP – stack pointer • ESI, EDI – index registers • EBP – extended frame pointer (stack) • Segment • CS – code segment • DS – data segment • SS – stack segment • ES, FS, GS - additional segments Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Some Specialized Register Uses (2 of 2) • EIP – instruction pointer • EFLAGS • status and control flags • each flag is a single binary bit Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

Status Flags • Carry • unsigned arithmetic out of range • Overflow • signed arithmetic out of range • Sign • result is negative • Zero • result is zero • Auxiliary Carry • carry from bit 3 to bit 4 • Parity • sum of 1 bits is an even number Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.

System Registers • IDTR (Interrupt Descriptor Table Register) • GDTR (Global Descriptor Table Register) • LDTR (Local Descriptor Table Register) • Task Register • Debug Registers • Control registers CR0, CR2, CR3, CR4 • Model-specific Registers

Floating-Point, MMX, XMM Registers • Eight 80-bit floating-point data registers • ST(0), ST(1), . . . , ST(7) • arranged in a stack • used for all floating-point arithmetic • Eight 64-bit MMX registers • Eight 128-bit XMM registers for single-instruction multiple-data (SIMD) operations Irvine, Kip R. Assembly Language for Intel-Based Computers 5/e, 2007.