Dynamic Power Noise Analysis Method for Memory Designs

150 likes | 338 Vues

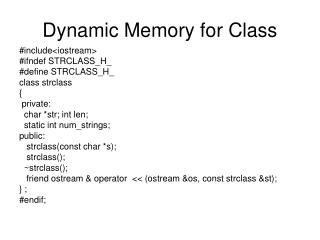

Dynamic Power Noise Analysis Method for Memory Designs. Chanseok Hwang , Changwoo Kang, Bosun Hwang Joonho Choi, Moonhyun Yoo CAE Team, Semiconductor Research Center Samsung Electronics. Outline. Memory Design Overview Memory Core Operations Our approach Memory Core Circuit Modeling

Dynamic Power Noise Analysis Method for Memory Designs

E N D

Presentation Transcript

Dynamic Power Noise Analysis Method for Memory Designs Chanseok Hwang, Changwoo Kang, Bosun Hwang Joonho Choi, Moonhyun Yoo CAE Team, Semiconductor Research Center Samsung Electronics

Outline • Memory Design Overview • Memory Core Operations • Our approach • Memory Core Circuit Modeling • Power Grid Creation and Reduction • Simulation Results • Conclusions

Memory Design Overview • Power noise increasingly affects circuit robustness • Low VDD (< 1.0V), High Speed (>2GHz) • Challenges in power noise analysis • Modeling of huge power network • Long simulation times An Example of DRAM Fullchip Power Grid

DRAM Core Operations • Core AC parameters : Sensing/Restore Time • Highly sensitive to power noises : Voltage margin and Operation speed VDD VCELL LAB VCELL = 1.125(90% VDD) VBL WL VBL=500mv BL LAB BLB Sensing time VSS LA Restore time Simulation waveforms of sensing operation Sense amplifiers with power networks

Our Approach • Current Source Model (CSM) • Core sub-array block is replaced by a current source • Multi-banks operation can be simulated • Power Network Generation & Reduction • Memory core power network is generated automatically • MOR technique is adopted efficiently

A C E G Active WL Block with active WL B D F H Active blocks become current sources Block with inactive WL SA SA SWD SWD Conj Conj Fullchip with 8 Banks Core Bank Sub-Array Block Inactive blocks become decoupling caps Hierarchical Memory Core Structure Current Source Modeling

A C E G B D F H Multiple-Bank Operations Activate Bank H Activate Bank F A C E G A C E G 7ns B D F H B D F H Activate Bank B, C, F, G Activate Bank A, D, E, H A C E G 10ns B D F H : current sources : circuits

Our Approach • Current Source Model (CSM) • Core sub-array block is replaced by a current source • Multiple-Bank Operation Modeling • Power Network Generation & Reduction • Memory core power network is generated automatically in early design stages • MOR technique is adopted efficiently

Coarse Grid Coarse Grid Coarse Grid Fine Grid Power Network Generation & Reduction Automatically Generated Power Network amp amp amp amp pad amp amp amp amp amp amp Power Network Generation GUI Reduced Power Network

A C E G B D F H Power Noise Verification Flow Active Circuits Current Sources + Power Network Creation Simulation Waveform Circuit connection to power network Circuit Simulation Voltage Drop Map Viewer Verification Fail

Simulation Results • Example Circuit: 1G DRAM • Sensing & Restore Time Comparisons • Simulation Time and Accuracy for the Proposed Power Network Model • Single Bank vs. Multiple Bank Operations

Results: Analysis of different power networks • Run-Time: 15.3X reduction • Accuracy Error:1% in Sensing, 8% in Restore time

Simulation Results • We could get this results by using the proposed method.

Conclusions • Current Source-based Model is proposed for the power noise analysis of memory circuits. • Based on the hierarchical memory core array structure • The method of automatic generation and reduction of power networks at design early stage is suggested. • In Simulation Results: 1G DRAM • Simulation time reduction > 15X • Analysis error < 8% • Due to the reduced complexity the simulation of multiple-bank operations was possible.