Asynchronous RISC Microprocessor Design and Implementation at Technion Israel

This project explores the benefits of asynchronous VLSI circuit design in implementing an ARM-based RISC microprocessor. Key advantages include eliminated clock skew, improved average performance, adaptability to variations, reduced power requirements, and lower noise levels. The architecture features a separate instruction and data memory, each supporting up to 64KB in little-endian format. The project utilizes Altera's APEX 20K FPGA, includes a PCI interface, and integrates a complete simulation of a data-path through the pipeline, focusing on out-of-order execution and effective branch decision-making.

Asynchronous RISC Microprocessor Design and Implementation at Technion Israel

E N D

Presentation Transcript

ARM – Asynchronous RISC Microprocessor הטכניון - מכון טכנולוגי לישראל המעבדה למערכות ספרתיות מהירות הפקולטה להנדסת חשמל Submitted by: Tziki Oz-Sinay, Ori Lempel Supervised by: Roni Mittleman

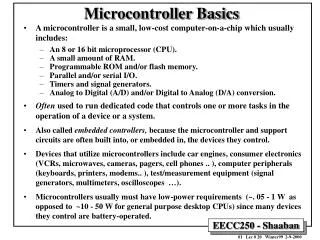

General Overview The benefits of asynchronous VLSI circuit design include: • Elimination of clock skew problems • Average case performance • Adaptivity to processing and environmental variations • Lower system power requirement • Reduced noise

Project Description Data Cache Inst Cache SDRAM 32MB SDRAM 32MB Program Code (assembler) Altera APEX 20K RS232 Watch Window (debug) PCI Interface

ARM Architecture • Register Set: The ARM provides 8 16-bit general-purpose data registers • Memory Management: • Separate instruction memory and data memory, each having an address space of up to 64Kbytes. • Both memory spaces are layed out in Little-Endian format.

Instruction Set 4 3 3 6 4 3 9 OpCode Rx Ry OpCode Rx Imm movi Rx, Imm addi Rx, Imm subi Rx, Imm mov Rx, Ry add Rx, Ry sub Rx, Ry or, Rx, Ry and Rx, Ry 4 3 3 6 4 12 OpCode Imm OpCode Rx Ry Imm jump Imm lw Rx, Ry, Imm sw Rx, Ry, Imm bez Rx, Ry, Imm

Out Of Order BranchDecision Op[3:0] ALU0PDst[3:0] Execute Retire Decode Rename Write Back Fetch Instruction Cache PDst[3:0] ALU0Res[15:0] SrcVal1[15:0] ALU1PDst[3:0] PC[15:0] Op[3:0] SrcVal2[15:0] ALU1Res[15:0] Date Cache LDst[3:0] LDst[3:0] Imm[11:0] VInst[15:0] Val15:0] LSrc[3:0] Op[3:0] DataIn[15:0] Imm[11:0] Inst[15:0] PDst[3:0] MemPDst[3:0] PDst[3:0] SrcVal1[15:0] DataOut[15:0] Addr[15:0] SrcVal2[15:0] ReadWrite# Imm[11:0] ARM Pipeline

Out-Of-Order Engine branches non-mem inst mem inst non-branch inst BranchDecision to IFU DATA CACHE ALU0 ALU1 RS0 RS1 Inst from ID ROB RAT RRF In Order Out of Order

Hardware Requirements • Gidel PROC20K card comprising: • Altera APEX 20K FPGA (type EP20K400) • 2*32MB SDRAM • Integrated PCI interface • RS232 port Software Requirements • Altera SignalTap2 embedded logic analyzer • ARM assembler

Timeline • 28/12/03(mid semester report): • Asynchronous simulation of IFU+ID based on Balsa code. • Synthesis of IFU+ID pending arrival of debug software. • Detailed translation of uarch to asynchronous enviornment (handshaking, arbitration protocols). • 4/3/04(final report, first semester): • Asynchronous simulation of a complete data-path flow through the pipeline: mov R0, 1 add R0, 1