Exploring PowerPC Architecture: Insightful Overview and Key Components

Learn about PowerPC, a RISC architecture jointly designed by Apple, IBM, and Motorola in the 1990s, ranging from embedded controllers to supercomputers. Dive into PowerPC families, pipeline structure, cache unit, sequencer unit, and more.

Exploring PowerPC Architecture: Insightful Overview and Key Components

E N D

Presentation Transcript

Chao Han ELEC6200 Computer Architecture PowerPC ELEC6200-001: Han: PowerPC

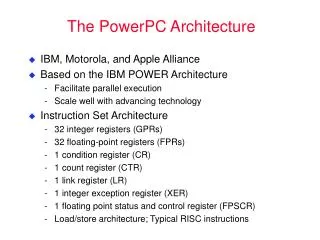

Introduction • PowerPC is a RISC architecture based on IBM's POWER (Performance Optimization With Enhanced RISC). • It was jointly designed by Apple, IBM, and Motorola by early 1990s. • Aim was to form the basis of a new generation of high-performance low-cost products ranging from embedded controllers to massively parallel supercomputers. • PowerPC 600 family, PowerPC 700 family, PowerPC 900 family, PowerPC 400. ELEC6200-001: Han: PowerPC

PowerPC 601 Architecture ELEC6200-001: Han: PowerPC

Pipeline Structure ELEC6200-001: Han: PowerPC

Instruction Queue and Dispatch Logic • It is Fed by eight-word bus from the cache. • During each cycle, the dispatch logic considers the bottom four entries of the instruction queue and dispatches up to three instructions. ELEC6200-001: Han: PowerPC

Branch Processing Unit ELEC6200-001: Han: PowerPC

Fixed-point execution unit ELEC6200-001: Han: PowerPC

Floating-point Execution Unit • Supports IEEE-754 FP data types For both single and double-precision floating-point arithmetic operations. ELEC6200-001: Han: PowerPC

Cache Unit & Memory Management Unit • 32 Kbytes • 8-way associative • Unified (instruction and data) • Capable of performing a complete read-modify- write every cycle • Performs the virtual to real address translation for load and store instructions • Acts as a backup for instruction fetch address translations • Provides support for segment oriented, page oriented and block oriented translations. ELEC6200-001: Han: PowerPC

Sequencer Unit • It is an embedded support processor that assists the core CPU in handling many of the algorithmic functions of the PowerPC architecture. • It contains 1) 1K entry microcode ROS (Read-Only-Storage) 2) 8 single word general purpose registers 3) 32 word Private RAM 4) control logic required to execute the robust 18 bit instruction set ELEC6200-001: Han: PowerPC

COP Unit • The Common On-chip Processor is the master control logic for the build-in self-test, debug and test features of the 601 chip. • It contains a linear feedback shift register (LFSR), a multiple input signature register (MISR) and the control logic required to sequence BIST operations. • It provides the capability to stop and start the internal clocks and to dump the state of all registers, RAMs and register files on the chip. ELEC6200-001: Han: PowerPC

PowerPC 601 ELEC6200-001: Han: PowerPC

References • http://www.kirps.com/web/main/_blog/all/a-short-history-of-the-powerpc-as-a-desktop-processor.shtml • Michael K. Becker, Michael S. Allen, Charles R. Moore, John S. Muhich, David P. Tuttle, "The Power PC 601 Microprocessor," IEEE Micro, vol. 13, no. 5, pp. 54-68, Sep/Oct, 1993 http://ieeexplore.ieee.org/search/wrapper.jsp?arnumber=238002 • Charles R. Moore, “The PowerPC 601 Microprocessor”, Compcon 1993 http://zmoore.net/PPC601%20Compcon93.pdf ELEC6200-001: Han: PowerPC